Mobile DRAM IP

Filter

Compare

63

IP

from

7

vendors

(1

-

10)

-

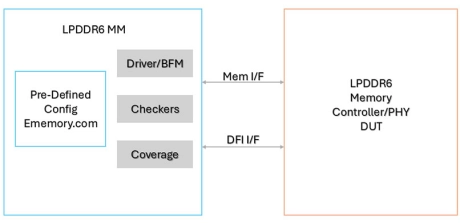

Simulation VIP for LPDDR6

- This Verification IP (VIP) is intended for modeling the upcoming JEDEC Low-Power Memory Device, LPDDR6 design specification.

- It provides a mature, highly capable compliance verification solution that supports simulation, formal analysis, and hardware acceleration platforms, making it applicable to intellectual property (IP), system-on-chip (SoC), and system-level verification.

-

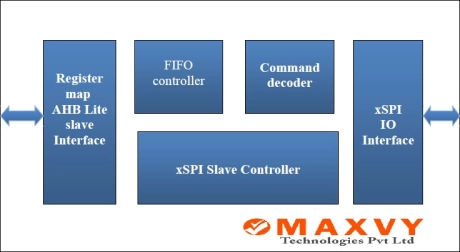

Expanded Serial Peripheral Interface (xSPI) Slave Controller

- The JESD251 Expanded Serial Peripheral Interface Slave controller is provides high data throughput, low signal count, and limited backward compatibility with legacy Serial Peripheral Interface(SPI) devices

- It is used to connect xSPI Master devices in computing, automotive, Internet of Things, Embedded system and mobile system processor to non-volatile memories, graphics peripherals, networking peripherals,FPGAs, sensors devices

-

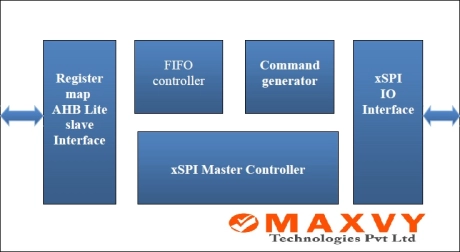

Expanded Serial Peripheral Interface (xSPI)Master Controller

- The Expanded Serial Peripheral Interface (JESD251) Master controller is low signal count, high data bandwidth, primarily for use in computing, automotive, Internet of Things, Embedded system and mobile system processor to connect multiple source of Serial Peripheral Interface (xSPI) slave devices like non-volatile memories, graphics peripherals, networking peripherals,FPGAs, sensors devices

-

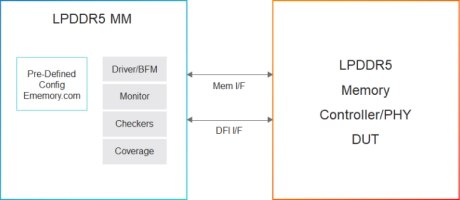

Simulation VIP for LPDDR5

- Speed

- 1066.5MHz (8533 Mbps)

- Device Density

- Supports a wide range of device densities from 2Gb to 32Gb

-

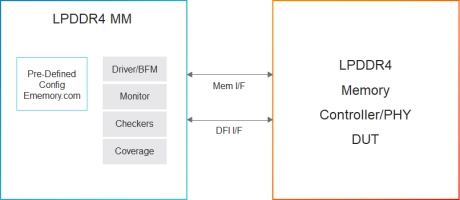

Simulation VIP for LPDDR4

- Speed (Mt/s)

- 2133MHz (4266MT/s)

- Device Density

- Supports a wide range of device densities from 4Gb to 32Gb

-

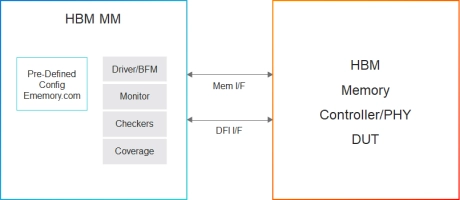

Simulation VIP for HBM

- Speed (MHz)

- 1800MHz (3.6 Gbps/pin)

- Device Density

- Supports a wide range of device densities from 1Gb to 24Gb

-

LPDDR5X PHY

- Supports High Data Rate

- Compliant with JEDEC LPDDR5X standards

- Scalable Architecture: Supports multiple channels and ranks, offering flexibility for various memory configurations

- Supports all auto calibrations

- Supports High Data Rate

-

DDR and LPDDR Combo PHY

- Supports multiple combinations of DDR/LPDDR interfaces

- Compliant with JEDEC DDR and LPDDR standards

- Supports all auto calibrations

- Industry leading area and power

-

LPDDR5/4/4X PHY - TSMC N7 for Automotive, ASIL B Random, AEC-Q100 Grade 2

- Supports JEDEC standard LPDDR5X, LPDDR5, LPDDR4 and LPDDR4X SDRAMs

- Support for data rates up to 6400 Mbps

- Designed for rapid integration with Synopsys’ LPDDR5/4/4X controller for a complete DDR interface solution

- DFI 5.0 controller interface

-

LPDDR5/4/4X PHY - TSMC N7

- Supports JEDEC standard LPDDR5X, LPDDR5, LPDDR4 and LPDDR4X SDRAMs

- Support for data rates up to 6400 Mbps

- Designed for rapid integration with Synopsys’ LPDDR5/4/4X controller for a complete DDR interface solution

- DFI 5.0 controller interface