Microsemi IP

Filter

Compare

38

IP

from

9

vendors

(1

-

10)

-

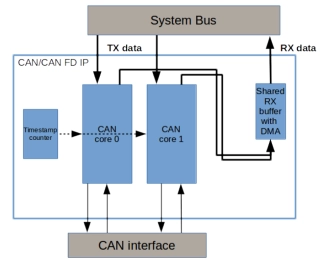

CAN 2.0/CAN FD IP core

- The IP is compliant to the new ISO 11898-1:2015 standard, supporting both standard CAN and CAN FD.

- The IP is available for most Xilinx, Altera, Lattice and Microsemi FPGA devices, supporting native bus interfaces like AXI, Avalon and APB. Processor integration is available for SOC type of FPGAs.

-

xSPI Multiple Bus Memory Controller

- SLL’s unified xSPI Multiple Bus Memory Controller IP supports the widest range of JEDEC xSPI and xSPI-like NOR Flash and PSRAM memories (JEDEC xSPI Profile 1.0 and 2.0, HyperBus 1.0, 2.0 and 3.0, OctaBus and Xccela Bus) that are available now from many memory vendors.

- JEDEC xSPI and xSPI-like memories offer good performance with lower hardware and power costs. Memory device variants offer up to 512 Mbit PSRAM, up to 2 Gigabit NOR Flash, up to 250 MHz DDR clock speeds, with x4, x8 and x16 data path widths, and a wide range of package options including 4mm x 4mm BGA49 and tiny WLCSP footprints. Some PRSAM devices are now also available with internal ECC.

-

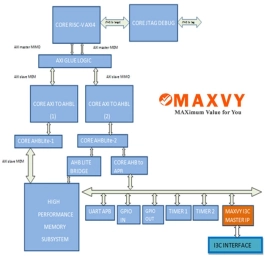

MIPI I3C Master RISC-V based subsystem

- RISC-V based MIPI I3C master interface has been developed to ease sensor system design architectures in mobile wireless products by providing a fast, low cost, low power, two-wire digital interface for sensors

- All the basic functionalities of MIPI I3C master has been proved with Microsemi smart fusion 2 creative development board .In addition the MIPI I3C master supports for both AHB lite and APB Interface

-

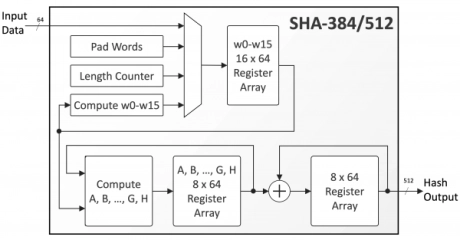

SHA-384 and SHA-512 Secure Hash Crypto Engine

- The SHA-384/512 is a high-throughput, and compact hardware implementation of the SHA-384 and the SHA-512 cryptographic hash functions provisioned by the FIPS180-4 standard.

- The core is designed for ease of use and integration and adheres to industry-best coding and verification practices.

-

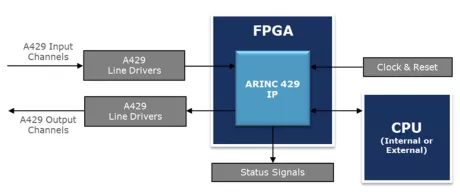

ARINC 429 IP-Core with DO-254 Package

- Applicable Standards:

- Configuration support per channel:

- Technical features:

- Supported tools:

-

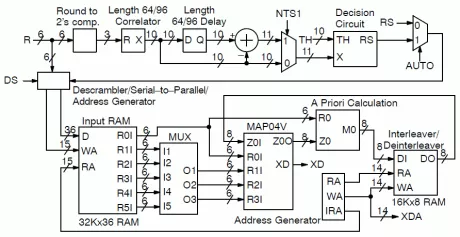

CCSDS turbo decoder with sync marker synchroniser, descrambler and input memory

- 16 state CCSDS compatible

- Rate 1/2, 1/3, 1/4 or 1/6

- Interleaver sizes from 1784 to 16056 bits

- Includes optional automatic synchronisation to non-inverted or inverted sync marker, optional descrambler and ping-pong input memory

-

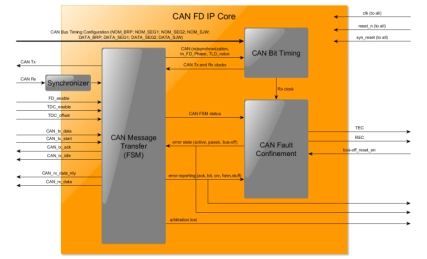

CAN FD Controller DO-254 IP Core

- The CAN FD Controller implements a Controller Area Network as specified in the ISO 11898:2015 Part 1, supporting both Classical and Flexible Data Rate CAN frame formats.

- The CAN FD Controller supports bit rates up to 1 Mbit/s for Classical CAN frame format and up to 10Mbit/s for Flexible Data Rate format.

-

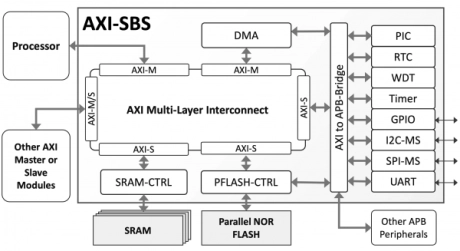

AXI Subsystem

- The AXI-SBS is an integrated, verified, AMBA® compliant hardware/software system ready for embedded applications using processors with AXI4 interfaces such as the BA20, BA21, and several RISC-V Implementations.

- The AXI Subsystem combines peripheral and interface IP cores with drivers and other essential software and an AXI/APB bus infra- structure.

-

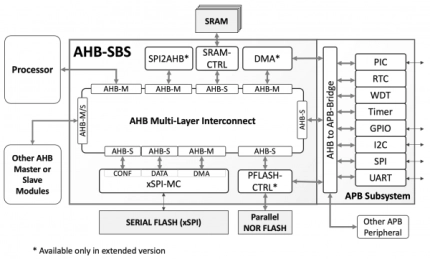

AHB Subsystem

- The AHB-SBS is an integrated, verified, AMBA® 3.0 interconnect and peripherals subsystem ready for embedded applications using processors with AHB bus interfaces such as the BA22-DE, BA22-CE, ARM Cortex-M0/M0+/M1/M3/M4, and several RISC-V processors.

- The AHB subsystem is available in two versions

-

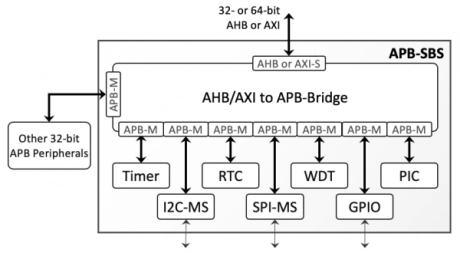

APB Subsystem

- The APB-SBS subsystem integrates typical microcontroller peripherals connected on the an AMBA® APB bus with a bridge to AHB or AXI bus.

- The subsystem is ready for integration with processors having either an AHB or an AXI interface such as the BA2x processors, and several ARM Cortex and RISC-V processors.

- The peripherals connect to the 32-bit APB ports of the APB bridge, which allows configuring the base address and the size of the address space for each peripheral. The subsystem includes the following modules: