MJPEG IP

Filter

Compare

9

IP

from

5

vendors

(1

-

9)

-

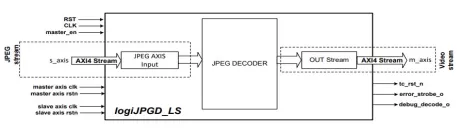

Lossless MJPEG Decoder

- Plug-and-Play IP core with Xilinx implementation tools (Vivado)

- Free reference designs available for AMD-Xilinx ZCU102 on request

-

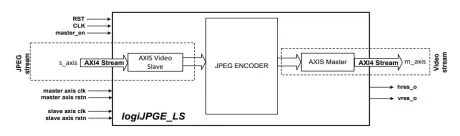

Lossless MJPEG Encoder

- Plug-and-Play IP core with Xilinx implementation tools (Vivado)

- Free reference designs available for AMD-Xilinx ZCU102 on request

-

Multi-Channel MJPEG Decoder

- Supports Xilinx® Zynq®-7000 AP SoC and 7 series FPGA families

- Compliant with the Baseline Sequential DCT mode of the ISO/IEC 10918-1 JPEG standard

-

M-JPEG Decoder

- Baseline DCT decoder according to JPEG ITU-T T.81 | ISO/IEC 10918-1 standard

- Seamless Motion JPEG (MJPEG) decoding

- Dual pixel output for top speed (4 pixels decoded every 3 cycles)

- Industry standard AXI interfaces (AXI and AXI4-stream for row-wise output)

-

M-JPEG Encoder (100 embedded quality levels)

- Baseline DCT compression (JPEG ITU-T T.81 | ISO/IEC 10918-1 with JFIF support)

- Industry standard AXI interfaces (AXI and AXI4-stream for row-wise inputs)

- Plug and Play IP blocks for Xilinx Vivado and Altera Quartus Qsys

- No need for external CPU or memory.

-

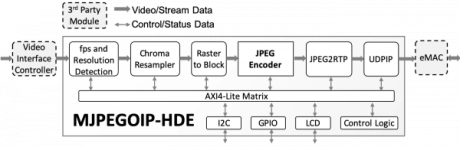

Motion JPEG Over IP – HD Video Encoder Subsystem

- This Video Over IP Subsystem employs JPEG compression and RTP/UDP/IP encapsulation to enable the rapid development of complete motion JPEG video streaming products. Hardware reference designs and customization services complete the solution.

- The subsystem uses CAST’s JPEG-E-S, JPEG2RTP, and UDPIP IP cores.

-

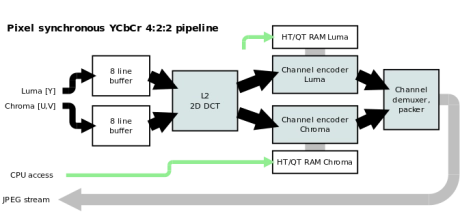

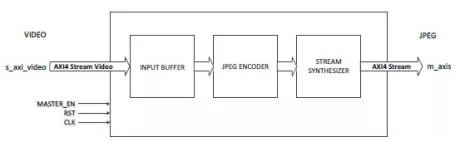

JPEG encoder

- Baseline JPEG compliant (ITU T.81), Motion JPEG

- Up to 12 bits depth possible (default: 8 bit)

- Super low latency (less than 1/10 of frame duration for rolling shutter cameras)

- Lossy compression by default

- Fully bit and cycle accurate co-simulation model available in Docker container

-

Motion JPEG Encoder

- Supports Xilinx® Zynq®-7000 AP SoC and 7 series FPGA families

- Compliant with the Baseline Sequential DCT mode of the ISO/IEC 10918-1 JPEG standard

-

Legacy formats decoder up to 1920X1080@60FPS

- The AL-D105 is a multi-format, multi-stream, video decoder IP core, capable of decoding 12 different video formats up to H.264/AVC 1920x1080i@60fps.

- The AL-D105 has been silicon proven in mutiple STB and DTV chipsets.