MIPI I3C Host Controller IP

Filter

Compare

32

IP

from

8

vendors

(1

-

10)

-

MIPI I3C Basic Master Controller

- MIPI I3C(Improved Inter Integrated Circuit) is a two-wire bidirectional serial Bus for sensors communication

- The MIPI I3C interface has been developed to ease sensor system design architectures in mobile sensor and IoT / automotive sensor wireless products by providing a fast, low cost, low power

-

MIPI I3C Basic v1.1.1 specifications with Host Controller Interface v1.1 specification

- Conforms to MIPI I3C v1.1 specifications

- MIPI Manufacturer ID: 0x03B3

- Dynamic Addressing while supporting Static Addressing for Legacy I2C Devices

- Legacy I2C messaging

-

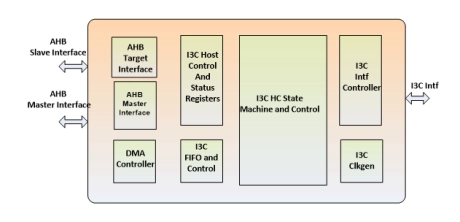

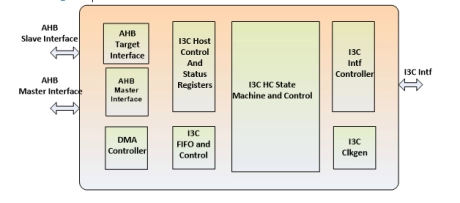

I3C Host Controller IP v1.2

- The I3C Host Controller IP implements Host Controller functionality as defined by the MIPI Alliance’s I3C Specification.

- The I3C bus is used for various sensors in the mobile/automotive system where the Host Controller transfers data and control between itself and various sensor devices.

- The I3C Host Controller IP Core provides a 32-bit AHB bus as the application interface to configure and control the I3C Host Controller IP Core.

-

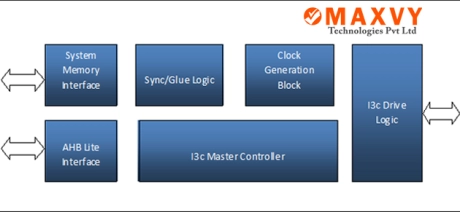

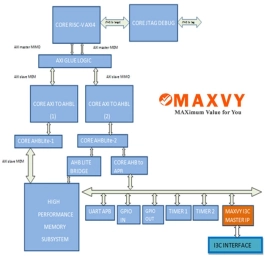

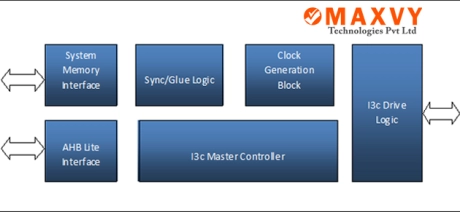

MIPI I3C Master RISC-V based subsystem

- RISC-V based MIPI I3C master interface has been developed to ease sensor system design architectures in mobile wireless products by providing a fast, low cost, low power, two-wire digital interface for sensors

- All the basic functionalities of MIPI I3C master has been proved with Microsemi smart fusion 2 creative development board .In addition the MIPI I3C master supports for both AHB lite and APB Interface

-

MIPI-I3C Master (SDR) RTL Design IP

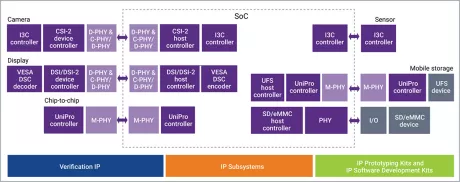

- MIPI I3C master Controller IP Core is fully compliant with the latest I3C specification and delivers high bandwidth and scalability for integration of multiple sensors into mobile, automotive and IoT system-on-chips (SoCs)

- The MIPI I3C master Controller supports in-band interrupts within the 2-wire interface provides significantly lower pin count, simplifying board design and reducing power and cost of the system The MIPI I3C master Controller IP is fully backward compatible with I2C, allowing designers to future proof their design, and the I3C controller IP operating modes enable systems with several ICs to efficiently connect to all sensors on a single I3C bus

-

MIPI I3C Controller and Target Functionality

- Supports MIPI I3C v1.1.1 specification

- Compliant with MIPI I3C Conformance Test Suite (CTS) v1.0

- Supports the MIPI I3C Host Controller Interface and DDR5 JEDEC JESD403-1 and System Management MCTP specifications

- Supports SDR, HDR-DDR, HDR-TSL/TSP; all data rates up to 33.4 Mbps

-

I3C 1.1 Host Controller

- The I3C Host Controller IP implements Host Controller functionality as defined by the MIPI Alliance’s I3C Specification.

- The I3C bus is used for various sensors in the mobile/automotive system where the Host Controller transfers data and control between itself and various sensor devices.

- The I3C Host Controller implements support for legacy I2C Device Controllers, Clock frequency scaling, Open-drain and Push-pull operation of I3C Interface, and Dynamic Addressing support.

-

MIPI I3C v1.1.1 Controller and Target

- Supports MIPI I3C v1.1.1 specification

- Compliant with MIPI I3C Conformance Test Suite (CTS) v1.0

- Supports the MIPI I3C Host Controller Interface and DDR5 JEDEC JESD403-1 and System Management MCTP specifications

- Supports SDR, HDR-DDR, HDR-TSL/TSP; all data rates up to 33.4 Mbps

-

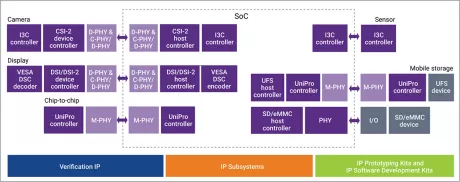

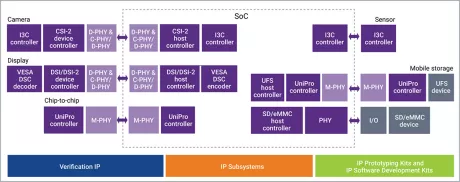

MIPI CSI-2 Host Controller

- Supports key features of the latest MIPI CSI-2 specification

- PPI interface to MIPI C-PHY v1.2 and D-PHY v2.1

- Programmable multi-lane merging

- Short and long packet format and all primary and secondary CSI-2 data formats

-

MIPI I3C v1.1.1 Basic Controller and Target

- Supports MIPI I3C v1.1.1 specification

- Compliant with MIPI I3C Conformance Test Suite (CTS) v1.0

- Supports the MIPI I3C Host Controller Interface and DDR5 JEDEC JESD403-1 and System Management MCTP specifications

- Supports SDR, HDR-DDR, HDR-TSL/TSP; all data rates up to 33.4 Mbps