MIPI HSI IP

Filter

Compare

12

IP

from

5

vendors

(1

-

10)

-

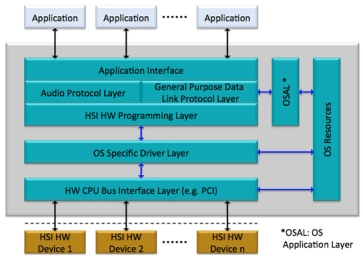

MIPI HSI Software Stack

- Compliant with MIPI HSI Specification version 1.0

- Portability in choice of OS, processors and hardware

- Easy-to-use interface for applications

- Fully documented generic device operation API

-

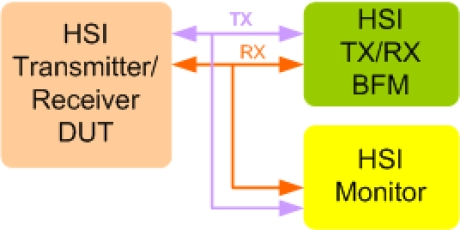

MIPI HSI Verification IP

- Supports 1.01 MIPI HSI Specification.

- Full MIPI HSI Tx and Rx functionality.

- Monitor,Detects and notifies the testbench of all protocol and timing errors.

- Supports data flow

-

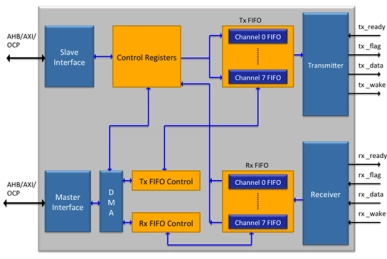

HSI Controller IP Core

- The High Speed Synchronous Serial Interface (HSI) Controller is used to provide high bandwidth, point-to-point, serial communication between two peers, like the cellular modem and application processor on a mobile platform, such as a smartphone or a tablet.

- The HSI Controller IP is designed to provide MIPI HSI 1.00 compliant connectivity to a SoC.

-

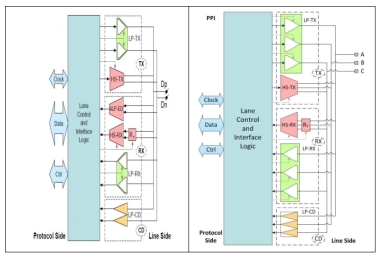

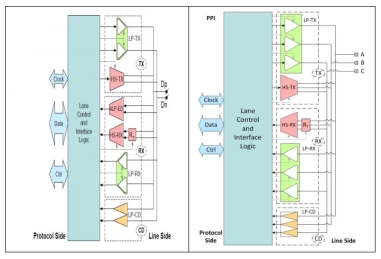

MIPI D-PHY℠ v2.5 IP Core

- This Tx/Rx transceiver complies with the MIPI Alliance C-PHY℠ v2.0 and D-PHY℠ v2.5 specifications, with world-class area and power dissipation, and is available for a range of foundry processes.

- This IP delivers 6 Gbps per lane for a max throughput of 24 Gbps in D-PHY℠ mode, and 6 Gsps per trio for a max throughput of 41.04 Gbps in C-PHY℠ mode.

-

MIPI C-PHY℠ v2.0 + D-PHY℠ v2.5 Combo IP Core

- This Tx/Rx transceiver complies with the MIPI Alliance C-PHY℠ v2.0 and D-PHY℠ v2.5 specifications, with world-class area and power dissipation, and is available for a range of foundry processes.

- This IP delivers 6 Gbps per lane for a max throughput of 24 Gbps in D-PHY℠ mode, and 6 Gsps per trio for a max throughput of 41.04 Gbps in C-PHY℠ mode.

-

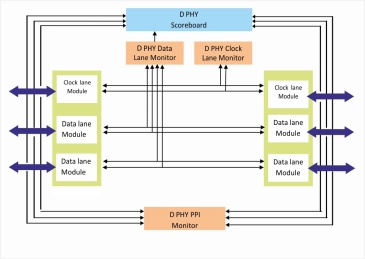

MIPI D-PHY Verification IP

- Compliant to MIPI D-PHY Specification Version 3.5 with PPI interface.

- Support HS-IDLE State between two data burst.

- Support for Alternate calibration Sequence & Preamble sequence.

- Supports all possible configuration for Data Lane Module and Clock Lane Module at PHY layer.

-

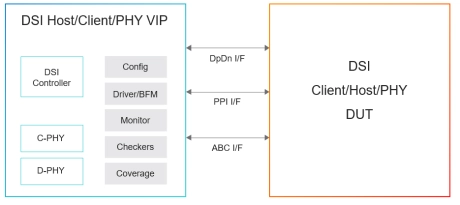

Simulation VIP for MIPI DSI-2

- Receiver and Transmitter Verification

- Verifies both DSI processor and peripheral

- Physical Layer

- Includes the MIPI D-PHYsm/C-PHYsm VIP for physical layer verification

-

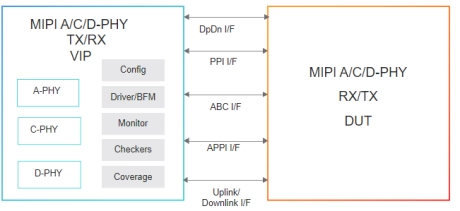

Simulation VIP for MIPI D-PHY, C-PHY and A-PHY

- PHY Monitor

- Built-in scoreboarding between serial/PPI interface, also monitors error signal interface

- Reports any detected error on any lane on serial interface and is not reflected on PPI interface

- C-PHY and D-PHY

-

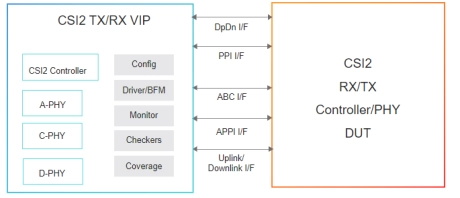

Simulation VIP for MIPI CSI-2

- Support testbench language interfaces for SystemVerilog, UVM, OVM, e, and SystemC

- Generates constrained-random bus traffic with predefined error injection at CSI-2, D-PHY, C-PHY and A-PHY levels

- Callbacks access at multiple TX and RX queue points for scoreboarding and data manipulation

-

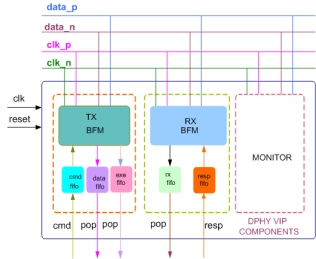

MIPI DPHY Verification IP

- Full MIPI DPHY Transmitter and Receiver functionality.

- Supports 3.0 MIPI DPHY Specifications.

- Supports both serial and PPI functionality testing.

- Supports short and long packets