MIPI DSI Controller IP

Filter

Compare

98

IP

from

11

vendors

(1

-

10)

-

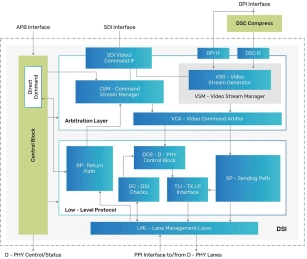

MIPI DSI Host Controller

- Compliant with the MIPI DSI and DSI-2 specifications, v2.1

- Support for dual MIPI DSI use case with VESA Display Stream Compression (DSC) v1.1 standard

- Support for video and command modes

- Wide PPI interface to C-PHY v1.2 and D-PHY v2.1

-

MIPI DSI TX Controller Subsystem

- Compliant with the MIPI DSI Interface Specification, rev. 1.3

- Standard PPI interface towards D-PHY

- 1-4 Lane Support

- Maximum Data Rate – 1.5 Gigabits per second

-

MIPI DSI TX Controller

- Compliant with MIPI DSI v1.3.1

- Supports both Command Mode and Video Mode

- Supports bi-directional low-power data transmission (LPDT)

- Cadence Serial Display Interface (SDI), MIPI Display Pixel Interface (DPISM), and Display Compression (DSC) input interface options

-

MIPI DSI Host Combo Controller

- Compliant with the MIPI DSI and DSI-2 specifications, v2.1

- Support for dual MIPI DSI use case with VESA Display Stream Compression (DSC) v1.1 standard

- Support for video and command modes

- Wide PPI interface to C-PHY v1.2 and D-PHY v2.1

-

MIPI DSI Transmitter v1.2 Controller IP, Compatible with MIPI D-PHY & C-PHY

- MIPI Alliance Specification for Display Serial

- MIPI display type 1, type 2, type 3 and type 4

- Video mode (Non-Burst with Sync Pulses, Non-Burst with Sync Events and same for Burst mode).

- TE feature (Tearing Effect) for command display

-

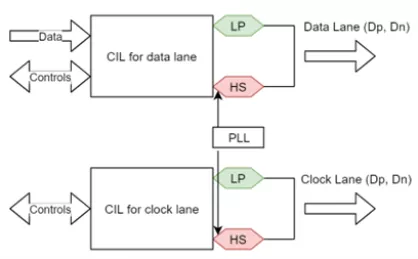

MIPI D-PHY TX PHY and DSI controller

- Scalability and Flexibility: Supports multiple data lanes for higher aggregate bandwidth, any of the multiple lanes can be configured into Clock Lane

- High Data Rates: Supports data transmission rates up to 4.5Gbps per lane, allowing for high-resolution displays and smooth refresh rates

- Energy Efficiency: Optimized for low power consumption, making it ideal for battery-powered devices

- Complete Solution: Combines the MIPI D-PHY Transmitter PHY and DSI Controller to make it a one-stop solution

-

MIPI C/D Combo TX PHY and DSI controller

- High Data Rates: Supports data transmission rates

- Energy Efficiency: Optimized for low power consumption, making it ideal for battery-powered devices

- Complete Solution: Combines the MIPI CD-PHY Transmitter PHY and DSI Controller to make it a one-stop solution

- Flexible IP Configuration

-

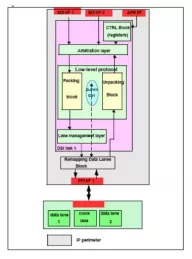

MIPI CD PHY Combo TX & RX + DSI & CSI Controller

- Our MIPI CD-PHY Transmitter and receiver PHY with Display Serial Interface (DSI) and Camera Serial Interface (CSI) Controllers are tailored for high-performance display and camera interface applications.

- These two PHY (TX and RX) integrated systems ensure seamless communication between the processor and display, the processor and camera; supporting high data rates and efficient power consumption.