MIPI CSI-3 IP

Filter

Compare

18

IP

from

6

vendors

(1

-

10)

-

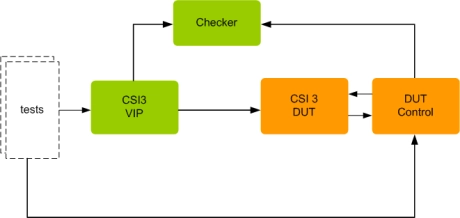

MIPI CSI-3 Verification IP

- Supports Version 1.2 MIPI CSI-3 Specification

- Supports transmission of Image frame

- Supports transmission of Attribute packets

- Supports Data transmission on multiple Virtual Channels

-

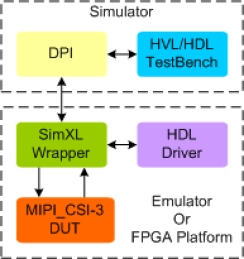

MIPI CSI-3 Synthesizable Transactor

- Supports Version 1.1 MIPI CSI-3 Specification

- Supports transmission of Image frame

- Supports transmission of Attribute packets

- Supports Data transmission on multiple Virtual Channels

-

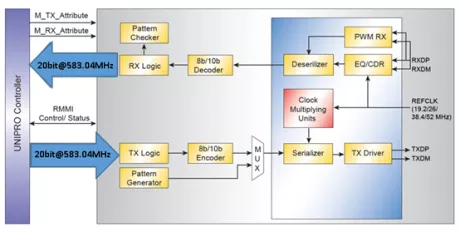

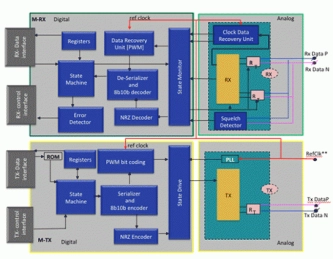

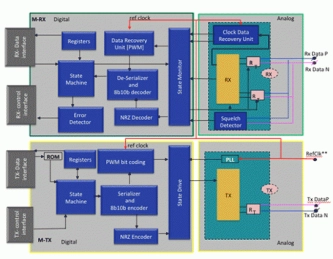

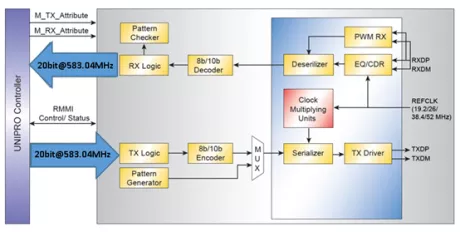

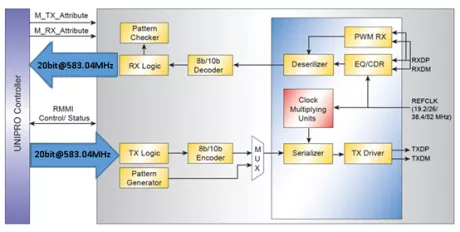

MIPI M-PHY® 3.1 Analog Transceiver

- The M-PHYs are of Type 1, which apply to UFS, LLI and CSI-3 protocols.

- The Multi-gear M-PHY 3.0 consists of analog transceivers, high speed PLL, data recovery units as well as the state-machine control — all in a single GDSII.

- The interface to the link protocol-specific controller (host or device) is compliant to the M-PHY RMMI specification, which allows seamless integration of the two IPs, namely the controller and the PHY, into the chip design.

-

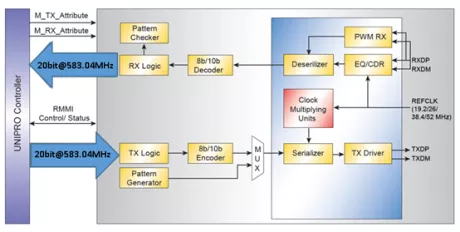

MIPI M-PHY® 4.1 Analog Transceiver

- The M-PHY is of Type 1, which apply to UFS, LLI, and CSI-3 protocols. The Multi-gear M-PHY 4.1 consists of analog transceivers, high-speed PLL, data recovery units as well as state-machine control — all in a single GDSII.

- The interface to the link protocol-specific controller (host or device) is compliant with the M-PHY RMMI specification, which allows seamless integration of the two IPs, namely the controller and the PHY, into the chip design.

-

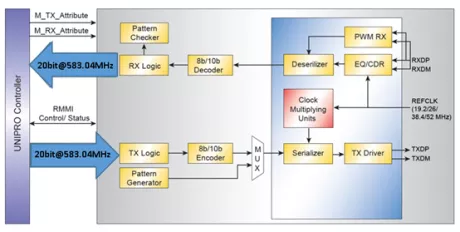

MIPI MPHY v3.1, 1Tx-1Rx Type-1, SMIC 40LL, N/S orientation

- Supports RMMI interface for applications such as UNIPRO protocol (UFS, CSI-3, DSI-2) and DigRF

- High speed gears, HS-G1A/B, HS-G2A/B and HS-G3A/B with scalable power consumptions

- Burst mode CDR with short sync length (< 16SI)

- Low speed PWM Gears from G1 to G4 with ultra-low power consumptions

-

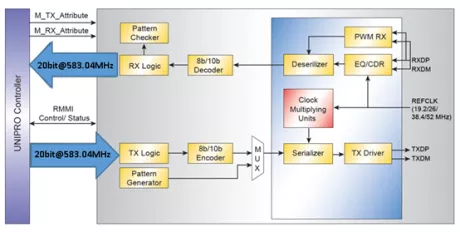

MIPI MPHY v3.1, 2Tx-2Rx Type-1, UMC 22ULL 1.8V, N/S orientation

- Supports RMMI interface for applications such as UNIPRO protocol (UFS, CSI-3, DSI-2) and DigRF

- High speed gears, HS-G1A/B, HS-G2A/B and HS-G3A/B with scalable power consumptions

- Burst mode CDR with short sync length (< 16SI)

- Low speed PWM Gears from G1 to G4 with ultra-low power consumptions

-

MIPI MPHY v3.1, 1Tx-1Rx Type-1, TSMC 55LP,

- Supports RMMI interface for applications such as UNIPRO protocol (UFS, CSI-3, DSI-2) and DigRF

- High speed gears, HS-G1A/B, HS-G2A/B and HS-G3A/B with scalable power consumptions

- Burst mode CDR with short sync length (< 16SI)

- Low speed PWM Gears from G1 to G4 with ultra-low power consumptions

-

MIPI MPHY v3.1, 2Tx-2Rx Type-1, TSMC 28HPC+, N/S orientation

- Supports RMMI interface for applications such as UNIPRO protocol (UFS, CSI-3, DSI-2) and DigRF

- High speed gears, HS-G1A/B, HS-G2A/B and HS-G3A/B with scalable power consumptions

- Burst mode CDR with short sync length (< 16SI)

- Low speed PWM Gears from G1 to G4 with ultra-low power consumptions

-

MIPI MPHY v3.1, 2Tx-2Rx Type-1, TSMC 16FFC, N/S orientation(ASIL-B)

- Supports RMMI interface for applications such as UNIPRO protocol (UFS, CSI-3, DSI-2) and DigRF

- High speed gears, HS-G1A/B, HS-G2A/B and HS-G3A/B with scalable power consumptions

- Burst mode CDR with short sync length (< 16SI)

- Low speed PWM Gears from G1 to G4 with ultra-low power consumptions

-

MIPI MPHY v3.1, 2Tx-2Rx Type-1, TSMC 12FFC, N/S orientation(ASIL-B)

- Supports RMMI interface for applications such as UNIPRO protocol (UFS, CSI-3, DSI-2) and DigRF

- High speed gears, HS-G1A/B, HS-G2A/B and HS-G3A/B with scalable power consumptions

- Burst mode CDR with short sync length (< 16SI)

- Low speed PWM Gears from G1 to G4 with ultra-low power consumptions