MIPI Automotive IP

Filter

Compare

325

IP

from

17

vendors

(1

-

10)

-

MIPI C-PHY v2.0 /D-PHY v2.5 Combo IP in TSMC

- Compliant with MIPI D-PHY spec up to v2.5 and C-PHY spec up to v2.0

- Support both MIPI DSI and CSI-2 protocols

-

MIPI C-PHY/D-PHY Combo v1.2 IP in TSMC(5nm, 7nm, 12/16nm, 28nm and 40nm)

- Fully compliant with MIPI D-PHY v1.2 and C-PHY v1.0 spec

- Supports MIPI CSI-2 protocol

-

MIPI D-PHY RX/TX v1.1 / v1.2 IP in TSMC (12/16nm, 28nm, 40nm, and 55nm process)

- Compliant with MIPI D-PHY specification up to v1.2/v1.1 (by different process nodes)

- Supports MIPI DSI and CSI-2 protocols

- Supports HS data rates up to 2.5Gbps (v1.2, per lane) . 1.5Gbps(v1.1, per lane)

- Supports LS data rate of 10Mbps and Ultra-low power modes

-

MIPI M-PHY v3.1 IP in TSMC(12/16nm, 28nm, 40nm, and 55nm)

- Supports RMMI interface for applications such as UNIPRO protocol (UFS, CSI-3, DSI-2) and DigRF

- High speed gears, HS-G1A/B, HS-G2A/B and HS-G3A/B with scalable power consumptions

- Burst mode CDR with short sync length (< 16SI)

- Low speed PWM Gears from G1 to G4 with ultra-low power consumptions

-

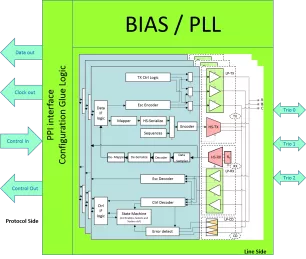

MIPI DSI-2 High Performance Device Combo Controller for Automotive

- Compliant with the MIPI DSI and DSI-2 specifications, v2.1

- Support for dual MIPI DSI use case with VESA Display Stream Compression (DSC) v1.1 standard

- Support for video and command modes

- Wide PPI interface to C-PHY v1.2 and D-PHY v2.1

-

MIPI DPHY Bidirectional 4 Lanes - GF 22FDSOI18, N/S, for Automotive, ASIL B Random, AEC-Q100 Grade 1

- Compliant with the MIPI D-PHY specification, v1.2

- Fully integrated hard macro

- Up to 2.5 Gbps per lane

- Aggregate throughput up to 10 Gbps in 4 data lanes

-

MIPI D-PHY Tx-Only 4 Lanes in TSMC (16nm) for Automotive

- Compliant with the MIPI D-PHY specification

- Fully verified hard macro

- Up to 2.5 Gb/s per lane

- Aggregate throughput up to 10 Gb/s in 4 data lanes

-

MIPI D-PHY Tx-Only 2 Lanes in TSMC (16nm) for Automotive

- Compliant with the MIPI D-PHY specification

- Fully verified hard macro

- Up to 2.5 Gb/s per lane

- Aggregate throughput up to 10 Gb/s in 4 data lanes

-

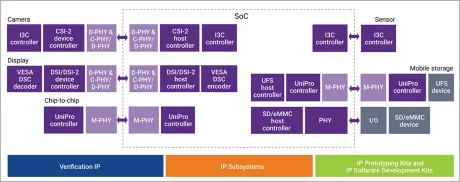

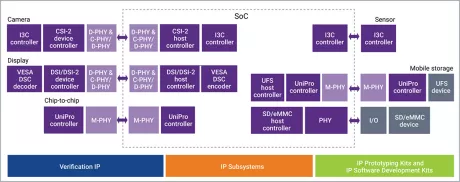

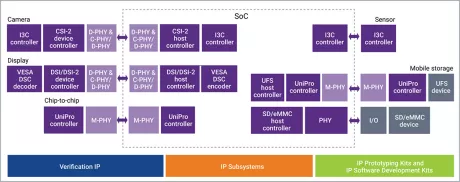

Automotive-grade MIPI CSI-2 host/device controllers for high-speed serial interface between image processor and camera sensors

-

MIPI M-PHY Type 1 G4 2TX2RX - TSMC N5A 1.2V, N/S, for Automotive, ASIL B Random, AEC-Q100 Grade 2

- Compliant with MIPI M-PHY v5.0 specification

- Supports MIPI UniPro, JEDEC UFS protocols

- Supports High-Speed (HS) Gear1,

- Gear2, Gear3, Gear4 and Gear5 A/B modes

- Supports M-PHY Type-I