Low Leakage SRAM Compiler IP

Filter

Compare

52

IP

from

8

vendors

(1

-

10)

-

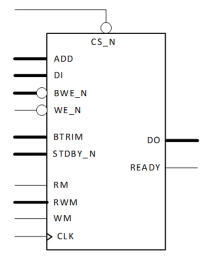

Single Port Low Leakage SRAM Memory Compiler on GF 22FDX+

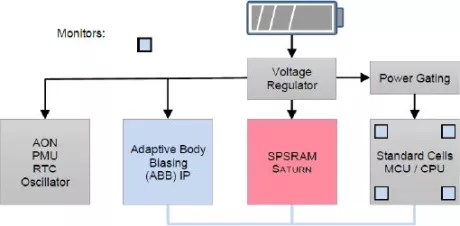

- Ultra-Low Leakage: High VT (HVT) and low leakage (LLHVT) devices are used with source biasing to minimize standby currents while operating at low voltage

- Bit Cell: Utilizes GlobalFoundries® Ultra-Low Leakage, 6T(L110) bit cells to ensure high manufacturing yields

- Five Power Modes: High Performance, Low Leakage, Standby, Retention, and Power Off modes provide flexibility for power optimization

-

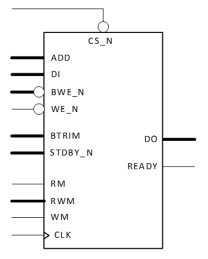

Single Port Low Leakage SRAM Memory Compiler on GF 22FDX+

- Ultra-Low Leakage: High VT (HVT) and low leakage (LLHVT) devices are used with source biasing to minimize standby currents while operating at low voltage

- Bit Cell: Utilizes GlobalFoundries® Ultra-Low Leakage 6T (P110UL) bit cells to ensure high manufacturing yields

- Five Power Modes: High Performance, Low Leakage, Standby, Retention, and Power Off modes provide flexibility for power optimization

- Speed Grades: Three options to adjust the speed/leakage balance and optimize for high speed or low power operation

-

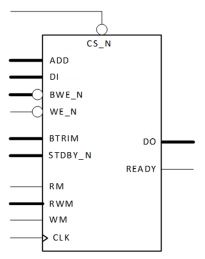

Single Port Low Leakage SRAM Memory Compiler on GF 22FDX

- Ultra-Low Leakage: High VT (HVT) and low leakage (LLHVT) devices are used with source biasing to minimize standby currents while operating at low voltage

- Bit Cell: Utilizes GlobalFoundries® Ultra-Low Leakage 6T (P110UL) bit cells to ensure high manufacturing yields

- Five Power Modes: High Performance, Low Leakage, Standby, Retention, and Power Off modes provide flexibility for power optimization

- Speed Grades: Three options to adjust the speed/leakage balance and optimize for high speed or low power operation

-

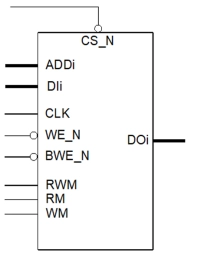

Single Port SRAM compiler - Memory optimized for ultra low leakage and high density - Dual Voltage - compiler range up to 640 k

- Available for Free Download and Use

- Source biasing implementation for ultra low leakage

- 4 times less leakage compared to stand by mode

- 3 times less leakage compared to retention mode

-

Single Port Low Voltage SRAM Memory Compiler on N22ULL - Low Power Retention and Column Repair

- Ultra-Low Leakage: High VT (HVT) are used to minimize leakage performance

- Bit Cell: Utilizes Low Leakage 6T bit cells to ensure high manufacturing yields

- Ultra Low Power Standby: Internally generated bias voltage for low leakage data retention

- Isolated Array and Periphery supplies: Periphery voltage can be shut off to further reduce standby power

-

Single Port Low Voltage SRAM Memory Compiler on N22ULL

- Ultra-Low Leakage: High VT (HVT) are used to minimize leakage performance

- Bit Cell: Utilizes Low Leakage 6T bit cells to ensure high manufacturing yields

- Ultra Low Power Standby: Internally generated bias voltage for low leakage data retention

-

Low Power Memory Compiler - Single Port SRAM - GF 22nm FDX

- Silicon proven Single Port SRAM compiler for GF22 FDX - Memory optimized for low power and supports body biasing.

-

Single Port SRAM compiler - Memory optimized for ultra low power and high density - Dual Voltage - compiler range up to 512 k

- Reduced die cost

- Pushed rule bit cell from foundry

- Ultra low power

- Low voltage operation down to 1.2 V

-

Single Port SRAM compiler - Memory optimized for ultra low power and high density - Dual Voltage - compiler range up to 512 k

- Reduced die cost

- Pushed rule bit cell from foundry

- Ultra low power

- Low voltage operation down to 1.2 V