Lattice IP

Filter

Compare

198

IP

from

19

vendors

(1

-

10)

-

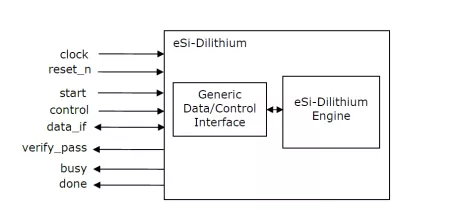

CRYSTALS Dilithium core for accelerating NIST FIPS 204 Module Lattice Digital Signature algorithm

- Hardware core for accelerating the high-level operations specified in the NIST FIPS 204 standard.

-

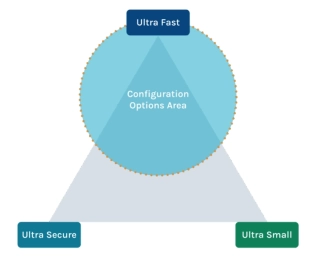

Highly configurable HW Lattice PQC ultra acceleration in AXI4 & PCIe systems

- PQPerform-Inferno is a powerful, scalable hardware solution engineered for unparalleled performance in the post-quantum era.

- As a FIPS 140-3 CAVP-certified product, it provides a trusted foundation for next-generation security.

-

Single instance HW Lattice PQC ultra accelerator

- PQPerform-Flare is a powerful hardware-based FIPS 140-3 CAVP-certified product, designed for high throughput and low latency PQC.

- It adds PQC for applications that typically handle a large number of transactions, such as high-capacity network hardware applications and secure key management HSMs.

-

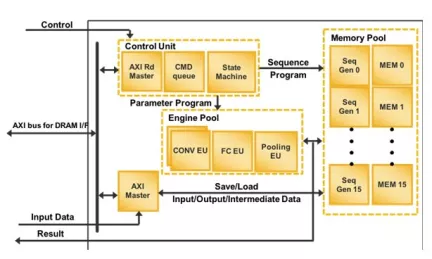

Convolutional Neural Network (CNN) Compact Accelerator

- Support convolution layer, max pooling layer, batch normalization layer and full connect layer

- Configurable bit width of weight (16 bit, 1 bit)

-

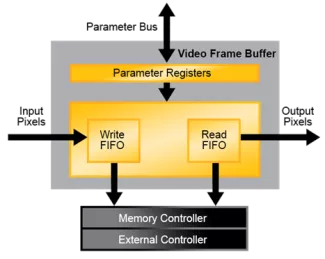

Video Frame Buffer

- Single color, YCbCr 4:2:2, YcbCr 4:4:4 and RGB video formats

- Input and output resolutions of 64x64 to 4Kx4K pixels

- Serial and parallel pixel processing

- Frame rate conversion

-

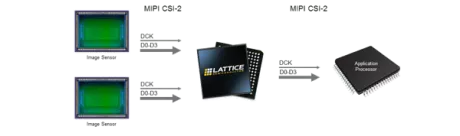

Two Input to One Output MIPI CSI-2 Camera Aggregator Bridge

- Supports MIPI CSI-2 inputs and outputs at up to 6 Gbps

- Combines two MIPI CSI-2 inputs to one MIPI CSI-2 output

- Supports all CSI-2 data types

- Compliance with MIPI D-PHY Specification v1.1

-

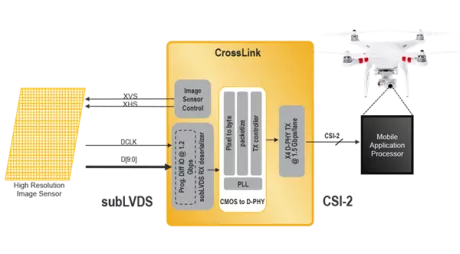

SubLVDS to MIPI CSI-2 Image Sensor Bridge

- Supports 4, 8, or 10 data lanes from Sony image sensor in 10-bit or 12-bit pixel widths

- Interfaces to MIPI CSI-2 Devices with 1 clock lane and 4 data lanes up to 6 Gbps total bandwidth

- Generates XVS & XHS for image sensors in slave mode operation

- Handles Sony IMX SubLVDS image sensors such as IMX236, IMX172, IMX178, IMX226, etc.

-

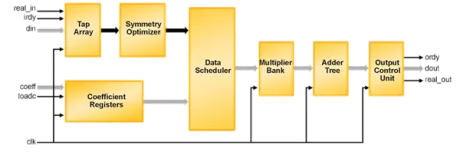

Serial FIR Filter

- Serial Arithmetic for Reduced Resource Utilization

- Variable Number of Taps up to 64

- Data and Coefficients up to 32 Bits

- Output Size Consistent with Data Size

-

RGB to MIPI DSI Display Interface Bridge

- Supports MIPI DSI and MIPI CSI-2 outputs up to 6 Gbp: 1, 2 or 4 data lanes

- Supports parallel MIPI DPI, CMOS, RAW and RGB interfaces at up to 300 MHz

- Supports CSI-2 compatible video formats (RAW, RGB, and YUV):

- Supports DSI compatible video formats (RGB):

-

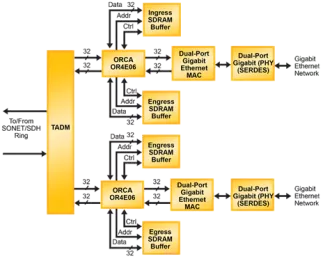

Quad GbE Over SONET/SDH

- Encapsulates GbE frames into SONET/SDH protocol using packet-over SONET (POS) and simplified data link (SDL)

- Quad OC-12c POS interface to the SONET/SDH network, each OC-12c carries one GbE data channel

- Performs all SONET/SDH section, line, and path termination functions

- Support for Jumbo Ethernet packets, up to 9.6 Kbytes