LPDDR4x IP

Filter

Compare

88

IP

from

12

vendors

(1

-

10)

-

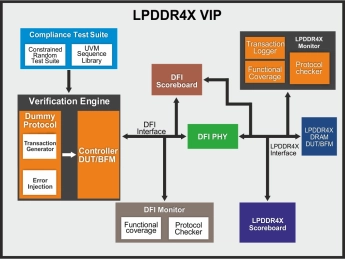

LPDDR4X Verification IP

- Compliant with JEDEC LPDDR4X Specification version JESD209-4-1.

- Supports LPDDR4X memory devices from all leading vendors.

- Supports multiple densities: 4Gb to 32Gb.

- Supports all lpddr4x ODT CA/CS/CKT control via MRS register

-

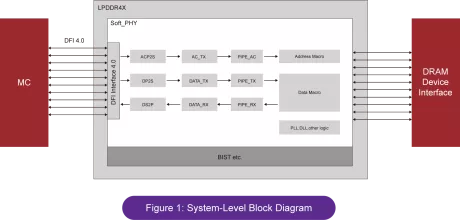

LPDDR4X PHY

- Compatible with LPDDR4X, with a maximum rate up to 4267Mbps

- Compliant with DFI 4.0 for PHY and control interfaces

- Flexible channel architecture

- Supports PHY-independent training mode using an embedded processor

-

LPDDR4X multiPHY - TSMC16FFC18

- Supports JEDEC standard LPDDR4X, LPDDR4, LPDDR3, DDR4, DDR3, and DDR3L (1.35V DDR3) SDRAMs

- Support for data rates up to 4,267 Mbps (process dependent)

- Designed for rapid integration with Synopsys Enhanced Universal DDR Memory/Protocol Controllers (uMCTL2/uPCTL2) for a complete DDR interface solution

- PHY independent, firmware-based training using an embedded calibration processor

-

LPDDR4X multiPHY - TSMC12FFC18

- Supports JEDEC standard LPDDR4X, LPDDR4, LPDDR3, DDR4, DDR3, and DDR3L (1.35V DDR3) SDRAMs

- Support for data rates up to 4,267 Mbps (process dependent)

- Designed for rapid integration with Synopsys Enhanced Universal DDR Memory/Protocol Controllers (uMCTL2/uPCTL2) for a complete DDR interface solution

- PHY independent, firmware-based training using an embedded calibration processor

-

LPDDR4X multiPHY - TSMC N7

- Supports JEDEC standard LPDDR4X, LPDDR4, LPDDR3, DDR4, DDR3, and DDR3L (1.35V DDR3) SDRAMs

- Support for data rates up to 4,267 Mbps (process dependent)

- Designed for rapid integration with Synopsys Enhanced Universal DDR Memory/Protocol Controllers (uMCTL2/uPCTL2) for a complete DDR interface solution

- PHY independent, firmware-based training using an embedded calibration processor

-

LPDDR4X multiPHY - TSMC N6

- Supports JEDEC standard LPDDR4X, LPDDR4, LPDDR3, DDR4, DDR3, and DDR3L (1.35V DDR3) SDRAMs

- Support for data rates up to 4,267 Mbps (process dependent)

- Designed for rapid integration with Synopsys Enhanced Universal DDR Memory/Protocol Controllers (uMCTL2/uPCTL2) for a complete DDR interface solution

- PHY independent, firmware-based training using an embedded calibration processor

-

LPDDR4X multiPHY - TSMC 16FFC18 for Automotive, ASIL B Random, AEC-Q100 Grade 2

- Supports JEDEC standard LPDDR4X, LPDDR4, LPDDR3, DDR4, DDR3, and DDR3L (1.35V DDR3) SDRAMs

- Support for data rates up to 4,267 Mbps (process dependent)

- Designed for rapid integration with Synopsys Enhanced Universal DDR Memory/Protocol Controllers (uMCTL2/uPCTL2) for a complete DDR interface solution

- PHY independent, firmware-based training using an embedded calibration processor

-

LPDDR4X multiPHY - SS 14LPP18

- Supports JEDEC standard LPDDR4X, LPDDR4, LPDDR3, DDR4, DDR3, and DDR3L (1.35V DDR3) SDRAMs

- Support for data rates up to 4,267 Mbps (process dependent)

- Designed for rapid integration with Synopsys Enhanced Universal DDR Memory/Protocol Controllers (uMCTL2/uPCTL2) for a complete DDR interface solution

- PHY independent, firmware-based training using an embedded calibration processor

-

LPDDR4X multiPHY - SS 11LPP

- Supports JEDEC standard LPDDR4X, LPDDR4, LPDDR3, DDR4, DDR3, and DDR3L (1.35V DDR3) SDRAMs

- Support for data rates up to 4,267 Mbps (process dependent)

- Designed for rapid integration with Synopsys Enhanced Universal DDR Memory/Protocol Controllers (uMCTL2/uPCTL2) for a complete DDR interface solution

- PHY independent, firmware-based training using an embedded calibration processor

-

LPDDR4X multiPHY - GF 14LPP18

- Supports JEDEC standard LPDDR4X, LPDDR4, LPDDR3, DDR4, DDR3, and DDR3L (1.35V DDR3) SDRAMs

- Support for data rates up to 4,267 Mbps (process dependent)

- Designed for rapid integration with Synopsys Enhanced Universal DDR Memory/Protocol Controllers (uMCTL2/uPCTL2) for a complete DDR interface solution

- PHY independent, firmware-based training using an embedded calibration processor