L2 Cache IP

Filter

Compare

105

IP

from

21

vendors

(1

-

10)

-

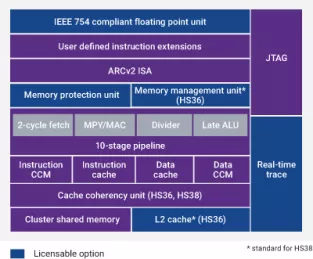

L2 cache option for multicore versions of ARC HS36 and HS38 processors

- Achieves up to 3232 DMIPS and 6681 CoreMarks* at 1.61 GHz on 28HPM (single-core configuration, worst case silicon and conditions)

- Delivers 2.13 DMIPS/MHz, 4.15 CoreMarks/MHz* (per core)

- High-speed, 10-stage pipeline

- Up to 16MB instruction and data close coupled memory (CCM)

-

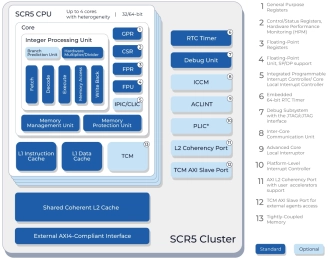

Efficient Linux-capable application core with a 9-stage in-order pipeline, an MMU, L1 and L2 caches, and cache coherency

- SCR5 is an efficient, silicon-proven, entry-level Linux-capable 32/64-bit RISC-V processor core.

- The SCR5 core fully supports RISC-V standard "I" Integer, "M" Integer Multiplication and Division, "A" Atomic, "C" 16-bit Compressed, "F" Single-Precision Floating-Point, "D" Double-Precision Floating-Point, “B” Bit Manipulation, and “K” Scalar Cryptography extensions.

-

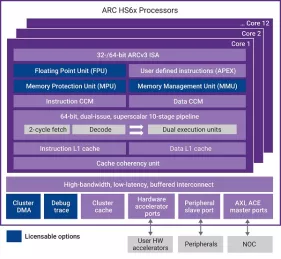

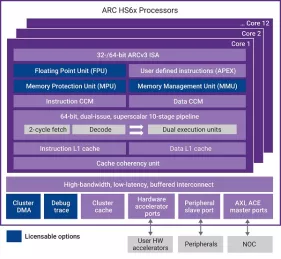

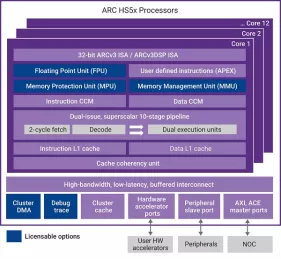

L2 cache/cluster shared memory option for multicore versions of ARC HS5x and HS6x processors

- Dual-issue, 64-bit processors for high-performance embedded applications

- 52-bit physical and 64-bit virtual addressing

- Up to 5400 DMIPS and 11,088 CoreMark per core at 1.8 GHz on 16FFC (worst case conditions, single-core configuration

- Multicore Processor versions with up to 12 CPU cores and up to 16 hardware accelerators

-

Efficient microcontroller core with a 5-stage in-order pipeline, privilege modes, an FPU, an MPU, L1 and L2 caches

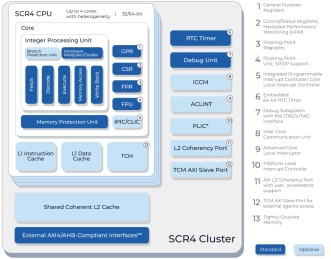

- SCR4 is a 32/64-bit RISC-V low-power, high-performance, area-optimized processor core with floating-point arithmetic functionality.

- The SCR4 core fully supports RISC-V standard "I" Integer, "M" Integer Multiplication and Division, "A" Atomic, "C" 16-bit Compressed, "F" Single-Precision Floating-Point, "D" Double-Precision Floating-Point, “B” Bit Manipulation, and “K” Scalar Cryptography extensions.

-

Efficient microcontroller core with a 5-stage in-order pipeline, privilege modes, an MPU, L1 and L2 caches

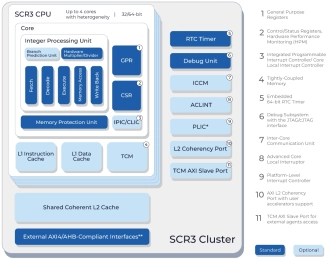

- SCR3 is an efficient, silicon-proven, microcontroller-class, 32/64-bit RISC-V processor core.

- It is optimized for power-sensitive, small-area, embedded applications, that demand high performance.

-

High-performance Linux-capable application core with a 12-stage dual-issue out-of-order pipeline, a VPU, cache coherency, and a hypervisor

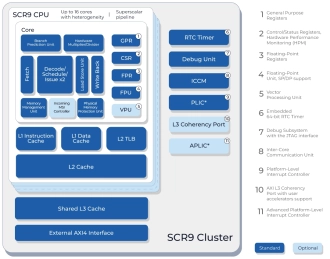

- SCR9 is a high-performance, silicon-proven, Linux-capable 64-bit RISC-V processor core for entry-level server-class applications and personal computing devices.

- The SCR9 core supports RISC-V standard "I" Integer, "M" Integer Multiplication and Division, "A" Atomic, "C" 16-bit Compressed, "F" Single-Precision Floating-Point, "D" Double-Precision Floating-Point, "V" Vector Operations, "B" Bit Manipulation, and "K" Scalar Cryptography extensions.

-

ARC HS66MP multi-core version of dual-issue HS66 with I and D cache for high-performance embedded applications

- Dual-issue, 64-bit processors for high-performance embedded applications

- 52-bit physical and 64-bit virtual addressing

- Up to 5400 DMIPS and 11,088 CoreMark per core at 1.8 GHz on 16FFC (worst case conditions, single-core configuration

- Multicore Processor versions with up to 12 CPU cores and up to 16 hardware accelerators

-

ARC HS57DMP multi-core version of dual-issue HS57D ARCv3DSP ISA, with I&D cache

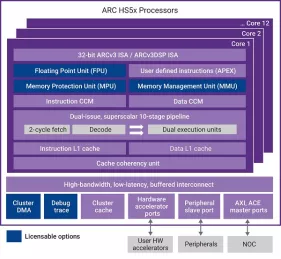

- Dual-issue, 32-bit processors for high-performance embedded applications

- Deliver up to 5400 DMIPS and 11,088 CoreMark per core at 1.8 GHz on 16FFC (worst case conditions, single-core configuration)

- Multicore Processor versions with up to 12 CPU cores and up to 16 hardware accelerators

- Based on advanced ARCv3 ISA

-

ARC HS57D 32-bit, dual-issue processor core and interconnect, ARCv3DSP ISA, with I&D cache

- Dual-issue, 32-bit processors for high-performance embedded applications

- Deliver up to 5400 DMIPS and 11,088 CoreMark per core at 1.8 GHz on 16FFC (worst case conditions, single-core configuration)

- Multicore Processor versions with up to 12 CPU cores and up to 16 hardware accelerators

- Based on advanced ARCv3 ISA