JESD204B SERDES IP

Filter

Compare

10

IP

from

4

vendors

(1

-

10)

-

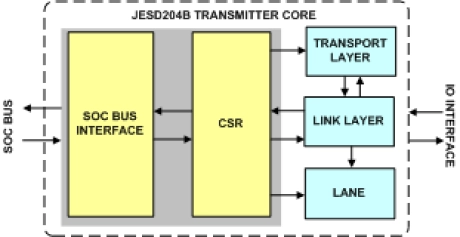

JESD204B Transmitter IIP

- Compliant with JESD204 specification JESD204A, JESD204B.01.

- Full JESD204B transmit functionality.

- Supports data rate upto 12.5 Gbps.

- Supports programmable clock frequency up to 12.5 GHz.

-

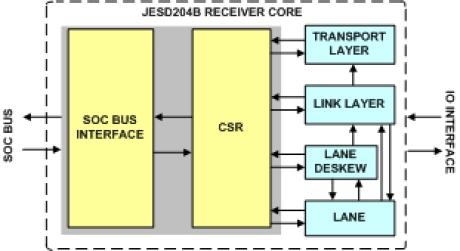

JESD204B Receiver IIP

- Compliant with JESD204 specification JESD204A, JESD204B.01.

- Full JESD204B receive functionality.

- Supports data rate upto 12.5 Gbps.

- Supports programmable clock frequency up to 12.5 GHz.

-

16G Multiproocol Serdes IP, Silicon Proven in TSMC 28HPC+

- Multiple lanes transceiver with data rate from 1Gbps to 16Gbps

- Transceiver version including both receiver and transmitter

- Transmitter only version

- 40bit/32bit/20bit/16bit selectable parallel data bus

-

MIPHY Consumer SerDes IP, Silicon Proven in ST 28FDSOI

- Consumer Application SERDES

- From 1.125Gb/s to 8Gb/s/ 10Gbs

- Technology: 28FDSOI 8ML & 10ML

- Support multi lane configuration

-

Multi-Rate Serdes IP Solution

- YouPHY-Serdes provides 2.5-32Gbps multi-rate SERDES IP which is designed for smooth integration of Multiple SERDES lanes demonstrate good performance class performance, area and power.

- The programmable PHY supports major standards such as PCIe Gen 4.0/3.0/2.0/1.0, USB 3.1/3.0, XAUI, SATA Gen 3.0/2.0/1.0, CEI-11G-LR, 10GBase-KX4, JESD204B, SGMII/QSGMII, RAPID I/O, HSSTP (Trace Port), V-By-One, DisplayPort and HMC.

-

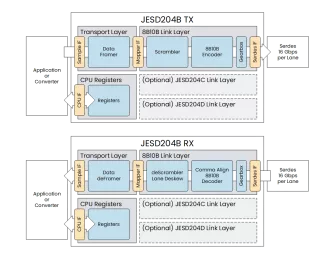

JESD204B Controller IP

- Designed to JEDEC JESD204B.01 specification

- Line rates from 1 Gbps to 12.5 Gbps (with optional extension to 16 Gbps)

- Supports 1-24 lanes

- Supports 1-96 converters

-

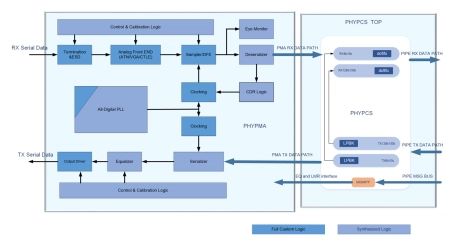

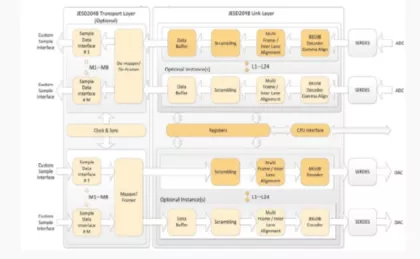

JESD204B Tx-Rx PHY IP, Silicon Proven in TSMC 65GP/55GP

- Widest feature set available in market.

- Scrambling and de-scrambling Included.

- High performance transport layer support.

- Build in test functions

-

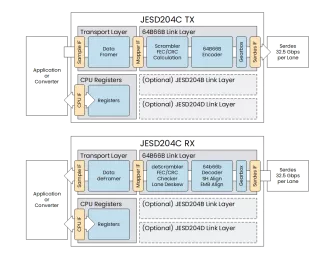

JESD204C Controller IP

- Designed to JEDEC JESD204C.1 specification

- Line rates from 1 Gbps to 32.5 Gbps

- Supports 1-24 lanes

- Supports 1-96 converters

-

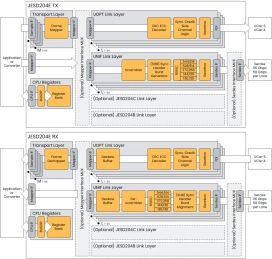

JESD204E Controller IP

- The JESD204E Controller IP from Chip Interfaces is an early adopter’s version of the upcoming revision of the JEDEC standard for Serial Interface for Data Converters.

- The JESD204-E IP core supports the UCIe Optimized Link Layer, a dedicated mode to run JESD over UCIe Modules with Line rates up the 64Gbps per bump, and a JESD204D backwards compatible mode called the Unified Link Layer with line speeds up to 116Gbps with PAM4 and 58Gbps with NRZ and full FEC support.

-

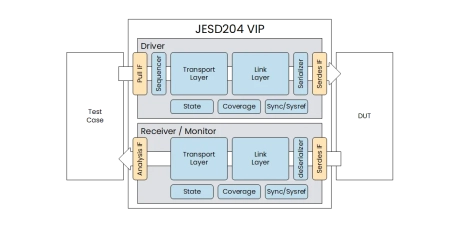

JESD204 Verification IP

- This JESD204 Verification IP provides an advanced and efficient solution for verifying and debugging these standards in a UVM simulation environment.

- The verification IP helps reduce time to test, accelerate verification process and ensures a high quality for the end-product.