Interleaver Deinterleaver IP

Filter

Compare

6

IP

from

6

vendors

(1

-

6)

-

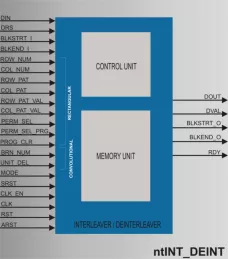

Interleaver / De-interleaver

- High-speed compact symbol interleaver/de-interleaver with AXI4-Stream interfaces

- Supports many popular standards such as DVB and CDMA2000

- Supports both the Forney Convolutional and the Rectangular Block architectures

- Supports a symbol size from 1 to 256 bits

-

Interleaver / De-interleaver

- Support for block or convolutional (de interleaving algorithm.

- Programmable interleaving or deinterleaving functionality.

- Parameterized symbol width and codeword length.

- Programmable block size, number or rows/columns.

-

HomePlug Turbo Decoder

- Supports rates½ and 16/18 coded input.

- FEC block size support : 16, 72, 136, 264, 520 bytes

- Configurable number of Iterations

- LLR width 14 bits

- Max-Log Map algorithm.VK-3052

- Compliant with HomePlug AV Specification Version 2.1

-

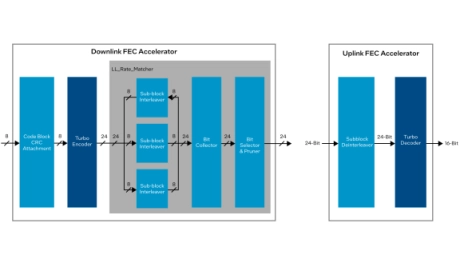

Turbo Intel® FPGA IP

- Forward-error correction (FEC) channel codes commonly improve the energy efficiency of wireless communication systems

- Turbo codes are suitable for 3G and 4G mobile communications and satellite communications

- You can use Turbo codes in other applications that require reliable information transfer over bandwidth- or latency-constrained communication links in the presence of data-corrupting noise. The 4G Turbo-V Intel® FPGA IP comprises a downlink and uplink accelerator for vRAN and includes the Turbo Intel® FPGA IP.

-

Interleaver/De-Interleaver

- High performance and area efficient symbol interleaver/de-interleaver

- Supports multiple standards, such as DVB, ATSC and IEEE 802.16

- Convolutional and rectangular block type architectures available

- Fully synchronous design using a single clock

-

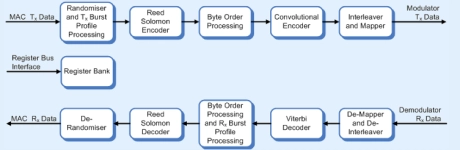

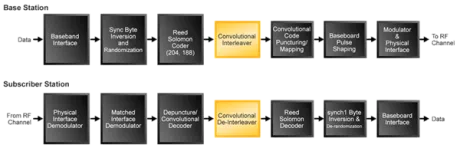

IEEE 802.16 WirelessMAN OFDM Channel Codec

- The CMS0005 802.16 Channel Codec provides all of the functionality necessary to implement the back end data processing in an 802.16a WirelessMAN-OFDM Phy Layer device.

- Its design has been carefully constructed to provide excellent FPGA performance without compromising the ASIC implementation in terms of area or speed.