Interleaved ADC IP

Filter

Compare

10

IP

from

7

vendors

(1

-

10)

-

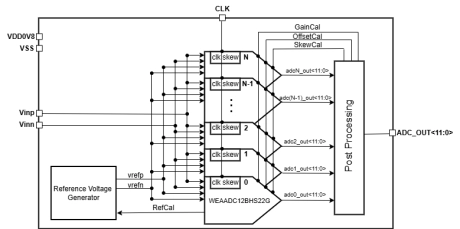

12-bit 2GSPS Time Interleaved ADC

- The WEAADC12BHSI22G is a 12-bit time interleaved Successive Approximation Analog-toDigital Converter (ADC) that supports both singleended and differential operation, depending on the input and reference connections

- It integrates 13 WEAADC12BHS22G with programmable clock skew (50ps coarse 4ps fine with minimum step 0.25ps) and pre/post-calibration logic on each

- Operating on a 0.8 V power supply, the WEAADC12BHSI22G can provide output up to 2GSPS in 13-interleaved mode

- The ADC can be clocked with 2GHz clock

-

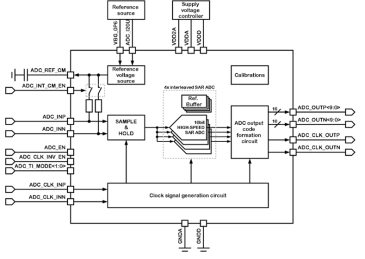

10-bit 1-channel 10 to 150 MSPS SAR ADC

- TSMC CMOS 55 nm

- Resolution 10-bit

- Conversion rate from 50 to 150 MSPS

-

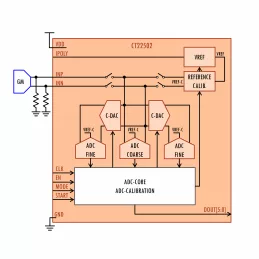

6b-1GSps SubRange Flash ADC

- 3-6bits, 1GSPS Sub-ranging AD Converter

- 0.9V Supply

- 600mV Differential Input

-

Rad Hard 12 bit ADC

- Successive Approximation Register (SAR), interleaved 8-fold

- 12 bit default nominal resolution

- 14 bit and 16 bit resolution by in-ADC transparent oversampling, resulting in 12 and 13 ENOB

- 0.7LSB noise, 0.7LSB DNL, 4LSB INL in nominal mode, @RT, BOL

-

12 bit ADC

- Successive Approximation Register (SAR), interleaved 8-fold

- 12 bit default nominal resolution

- 14 bit and 16 bit resolution by in-ADC transparent oversampling, resulting in 12 and 13 ENOB

- 0.7LSB noise, 0.7LSB DNL, 4LSB INL in nominal mode, @RT, BOL

-

Cryogenic 12 bit ADC

- Successive Approximation Register (SAR), interleaved 8-fold

- 12 bit default nominal resolution

- 14 bit and 16 bit resolution by in-ADC transparent oversampling, resulting in 12 and 13 ENOB

- 0.7LSB noise, 0.7LSB DNL, 4LSB INL in nominal mode, @RT, BOL

-

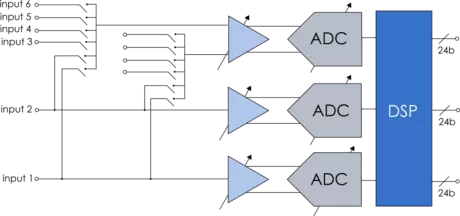

14-bit, 4.32Gsps Ultra high speed Wideband, Time-Interleaved Pipeline ADC IP

- 14-bit Time-Interleaved Pipeline ADC

- 4.32GSps Sampling Rate

- 60dBFS SNR (9.7 ENOB) with 54MHz

- External AC coupling for the input signal

-

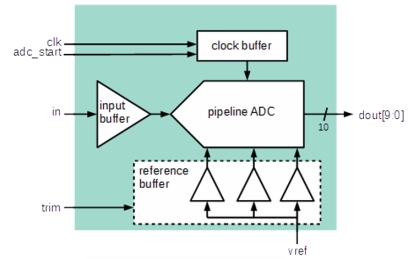

10 Bit 40 MS/s Pipeline ADC on AMS C18

- The IP consists of a 10 bit 40 MS/s pipeline ADC. A time-interleaved architecture with 1.5 bit per stage is used.

- The operational amplifiers are shared between the interleaved stages for reduced power consumption.

- The interleaving is transparent for the application.

-

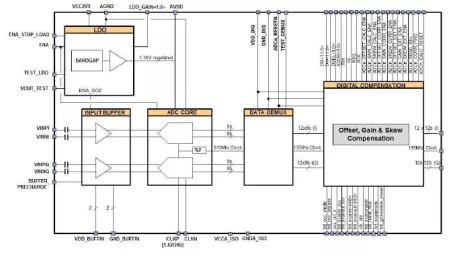

Dual core I & Q Analog to Digital Converter

- Maturity MAT05

- 9-bits DUAL-CORE I & Q SAR ADC

- Up to 1.62Gsps Sampling Rate

- Analog power supply for Input Buffer: from 1.7V to 2.75V (GO2 domain)

-

Ultra low-power Microphone, Audio, IoT interface

- Complete ultra low-power microphone/audio/IoT interface + ADC

- 140uW interface + 200uW ADC power