ISO 26262 ASIL D Certified RISC-V Processor IP

Filter

Compare

4

IP

from

2

vendors

(1

-

4)

-

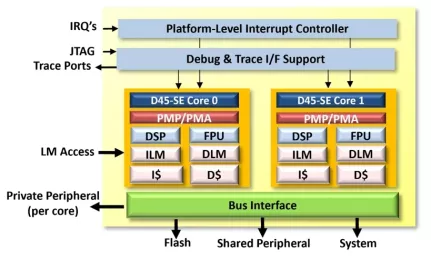

8-stage superscalar processor that supports ISO 26262 ASIL (Automotive Safety Integrity Level) -D level functional safety for automotive applications

- The 32-bit D45-SE is an 8-stage superscalar processor that supports ISO 26262 ASIL (Automotive Safety Integrity Level) -D level functional safety for automotive applications.

-

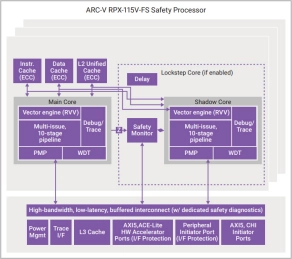

ARC-V RPX Series Functional Safety Processor IP

- The ARC-V™ RPX-110 series functional safety (FS) processors, which include the RPX-110-FS, RPX-115-FS, RPX-110V-FS, and RPX-115V-FS processors simplify development of high-performance safety-critical applications and accelerate ISO 26262 certification for automotive system-on-chips (SoCs).

- The Automotive Safety Integrity Level (ASIL) D compliant processors feature a pre-verified dual-core lockstep implementation including an integrated safety monitor.

- Additionally, they offer the flexibility to operate in an independent “hybrid” mode for ASIL B or non-automotive applications that demand higher performance from the same design.

-

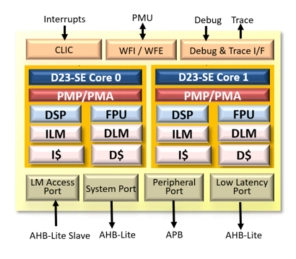

ISO26262 ASIL-B/D Compliant 32-bit RISC-V Core

- The AndesCore™ D23-SE is a 32-bit 3-stage pipeline CPU IP core based on AndeStar™ V5 architecture for embedded applications with small gate count, and some dual-issue ability.

- In addition to commonly used RISC-V IMAC, single/double precision FPU and DSP extensions, it supports the recently ratified ISA extensions such as B (bit manipulation), K (scalar cryptography), CMO (cache management operations) as well as Zce (code size reduction), plus Andes Custom Extension™ (ACE) for user-defined instructions.

-

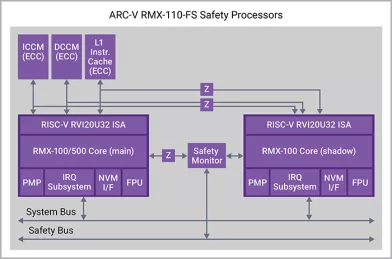

ARC-V RMX Series Functional Safety Processor IP

- Developed for full ASIL D compliance (systematic and random faults)

- Tightly-coupled dual-core safety implementation based on ultra-compact ARC-V RMX processors

- Single solution support for safety level up to ASIL D; Supports both ASIL D lockstep operation or ASIL B single-core operation (RMX-510-FS only)

- Integrated hardware safety features including ECC, user-programmable windowed watchdog timer, end-to-end protection (E2E) for buses/data-path, and lockstep safety monitor