HiGig MAC IP

Filter

Compare

1

IP

from

1

vendors

(1

-

1)

-

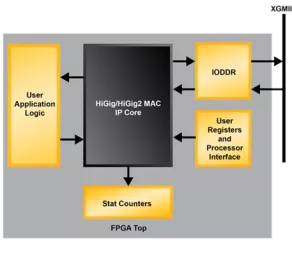

HiGig Ethernet MAC

- Compliant to the Broadcom HiGig and HiGig2 Protocol Definitions

- 64-bit wide internal data path operating at a maximum frequency of 187.5 MHz (LatticeECP3 maximum 156 MHz)

- XGMII interface to the PHY layer (using IODDR external to the core)

- XAUI interface to the PHY layer (using PCS/SERDES external to the core)