HDLC SDLC IP

Filter

Compare

6

IP

from

5

vendors

(1

-

6)

-

Used for controlling HDLC/SDLC transmission protocols

- Two separate receiver and transmitter interfaces.

- Two separate, configurable FIFO buffers for receiver and transmitter

- Bit stuffing and unstuffing

- Address recognition for receiver and address insertion for transmitter

-

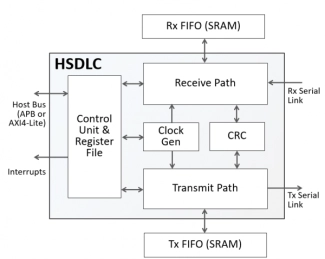

HDLC & SDLC Protocol Controller

- The HSDLC IP core implements a controller for the High-Level Data Link Control (HDLC) and the Synchronous Data Link Control (SDLC) protocols.

- It is based on the Intel® 8XC152 Global Serial Channel (GSC) working in SDLC mode, and adds features to support HDLC or proprietary frame transmission under host processor control.

- The core operates as a peripheral to a host processor, and is easy to integrate with both modern and legacy processors.

-

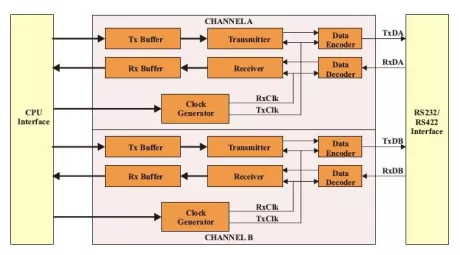

UART Core with SDLC Function

- Software compatible with Z85C30

- Dual Channel: A, B

- Configuration capability

- Asynchronous mode:

-

Enhanced Multiprotocol Serial Communication Controller

- Rapid prototyping and time-to-market reduction

- Design risk elimination

- Development costs reduction

-

8530 Multi-Protocol Controller

- Hardware features

- Communication protocol features

- Encode/decode of NRZ (Non-Return to Zero)

-

8530 - Serial Communication Controller

- Product Features

- Synchronous / Isosynchronous data rates

- Asynchronous capabilities

- Synchronous capabilities