HBM PHY IP

Filter

Compare

84

IP

from

18

vendors

(1

-

10)

-

TSMC CLN5FF HBM PHY IP

- High Bandwidth Memory (HBM) DRAM PHY

- Supports HBM 3.6Gbps

- Supports DFI 1:2

- Supports only BL4

-

TSMC CLN16FFGL+ HBM PHY IP

- High Bandwidth Memory (HBM) DRAM PHY

- Supports HBM 2Gbps

- Supports DFI 1:2

- Supports only BL4

-

TSMC N5A SD/eMMC PHY AG2 Platform

- Synopsys SD/eMMC PHY provides an optimal balance for cost and performance for storage solutions

- Synopsys SD/eMMC PHY is a hard IP that can be used to implement a single interface that can accomplish 4-bit, 8-bit eMMC & 4-bit SD operations

- It includes an optional digi logic circuitry which is required for high-speed operations

- It complies with eMMC 5.1 (JESD84-B51A) and SDIO 6.0 JEDEC standards

-

TSMC N3P SD/eMMC PHY North/South Poly Orientation MS add-on

- Synopsys SD/eMMC PHY provides an optimal balance for cost and performance for storage solutions

- Synopsys SD/eMMC PHY is a hard IP that can be used to implement a single interface that can accomplish 4-bit, 8-bit eMMC & 4-bit SD operations

- It includes an optional digi logic circuitry which is required for high-speed operations

- It complies with eMMC 5.1 (JESD84-B51A) and SDIO 6.0 JEDEC standards

-

TSMC N3P SD/eMMC PHY North/South Poly Orientation

- Synopsys SD/eMMC PHY provides an optimal balance for cost and performance for storage solutions

- Synopsys SD/eMMC PHY is a hard IP that can be used to implement a single interface that can accomplish 4-bit, 8-bit eMMC & 4-bit SD operations

- It includes an optional digi logic circuitry which is required for high-speed operations

- It complies with eMMC 5.1 (JESD84-B51A) and SDIO 6.0 JEDEC standards

-

TSMC N3E SD/eMMC PHY North/South Poly Orientation

- Synopsys SD/eMMC PHY provides an optimal balance for cost and performance for storage solutions

- Synopsys SD/eMMC PHY is a hard IP that can be used to implement a single interface that can accomplish 4-bit, 8-bit eMMC & 4-bit SD operations

- It includes an optional digi logic circuitry which is required for high-speed operations

- It complies with eMMC 5.1 (JESD84-B51A) and SDIO 6.0 JEDEC standards

-

TSMC N3A SD/eMMC PHY AG2 North/South Poly Orientation

- Synopsys SD/eMMC PHY provides an optimal balance for cost and performance for storage solutions

- Synopsys SD/eMMC PHY is a hard IP that can be used to implement a single interface that can accomplish 4-bit, 8-bit eMMC & 4-bit SD operations

- It includes an optional digi logic circuitry which is required for high-speed operations

- It complies with eMMC 5.1 (JESD84-B51A) and SDIO 6.0 JEDEC standards

-

Samsung 8LPU 1.8V/3.3V SD/eMMC PHY AP1

- Synopsys SD/eMMC PHY provides an optimal balance for cost and performance for storage solutions

- Synopsys SD/eMMC PHY is a hard IP that can be used to implement a single interface that can accomplish 4-bit, 8-bit eMMC & 4-bit SD operations

- It includes an optional digi logic circuitry which is required for high-speed operations

- It complies with eMMC 5.1 (JESD84-B51A) and SDIO 6.0 JEDEC standards

-

Samsung 5LPE 1.8V/3.3V SD/eMMC PHY AP2

- Synopsys SD/eMMC PHY provides an optimal balance for cost and performance for storage solutions

- Synopsys SD/eMMC PHY is a hard IP that can be used to implement a single interface that can accomplish 4-bit, 8-bit eMMC & 4-bit SD operations

- It includes an optional digi logic circuitry which is required for high-speed operations

- It complies with eMMC 5.1 (JESD84-B51A) and SDIO 6.0 JEDEC standards

-

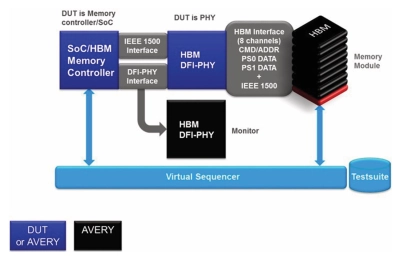

Verification IP for HBM

- HBM VIP is a comprehensive memory VIP solution portfolio for high bandwidth memory (HBM), targeting a new standard in memory performance, density, power consumption, and cost.

- HBM VIP is intended for SoC and memory control ler designers who employ external HBM modules and PHY developers to ensure both comprehensive verification and protocol and timing compliance.