Graphics Accelerator IP

Filter

Compare

19

IP

from

9

vendors

(1

-

10)

-

Scalable 3D Graphics Accelerator

- Graphics accelerator IP core designed to support the OpenGL® ES 1.1 API*

- Supports Xilinx® Zynq-7000 Ap SoC, 7 Series, Spartan®-6 and Virtex®-6

- Conformant to the ARM® AMBA® AXI4 bus

- FPGA resource-effective 3D acceleration

-

Bitmap 2.5D Graphics Accelerator

- Supports fast graphics operations with bitmaps

- 2.5D option enables perspective correct texture rendering in 3D

- Solid fill - Rectangle or Triangle rendering with any color

- Fully embedded into Xilinx® XPS and the EDK

-

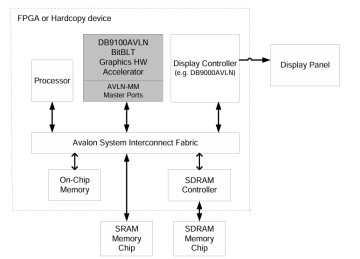

BitBLT Graphics Hardware Accelerator (Avalon Bus)

- The DB9100AVLN BitBLT Graphics Hardware Accelerator Verilog IP Core renders a graphics frame by generating new bitmaps from commands to combining existing bitmaps on and off-screen using one of 256 Raster Operations.

- A Raster Operation (ROP) is a bitwise Boolean operation (such as AND, OR, XOR, NOT).

-

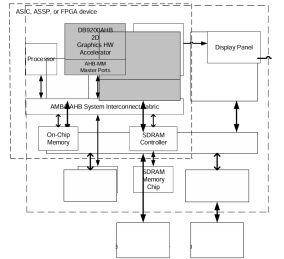

2D Graphics Hardware Accelerator (AHB Bus)

- Generates bitmaps from graphics instructions as well as combining existing bitmaps on and off-screen using one of 256 Raster Operations. A Raster Operation (ROP) is a bitwise Boolean operation (such as AND, OR, XOR, NOT) which lay the foundation for power hardware graphics primitive operations

- Generates characters from compressed bitmaps using its FONT Bitmap Color Expansion Unit

- Performs Alpha Blend operations of bitmaps with its Alpha Blend unit

- Draws lines, polygons, circles using its hardware efficient & pixel accurate Bresenham Algorithm Line Drawing Unit

-

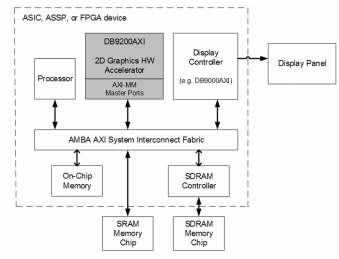

2D Graphics Hardware Accelerator (AXI Bus)

- Generates bitmaps from graphics instructions as well as combining existing bitmaps on and off-screen using one of 256 Raster Operations. A Raster Operation (ROP) is a bitwise Boolean operation (such as AND, OR, XOR, NOT) which lay the foundation for power hardware graphics primitive operations

- Generates characters from compressed bitmaps using its FONT Bitmap Color Expansion Unit

- Performs Alpha Blend operations of bitmaps with its Alpha Blend unit

- Draws lines, polygons, circles using its hardware efficient & pixel accurate Bresenham Algorithm Line Drawing Unit

-

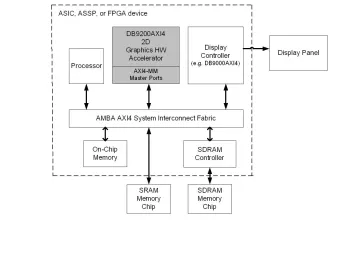

2D Graphics Hardware Accelerator (AXI4 Bus)

- Generates bitmaps from graphics instructions as well as combining existing bitmaps on and off-screen using one of 256 Raster Operations. A Raster Operation (ROP) is a bitwise Boolean operation (such as AND, OR, XOR, NOT) which lay the foundation for power hardware graphics primitive operations

- Generates characters from compressed bitmaps using its FONT Bitmap Color Expansion Unit

- Performs Alpha Blend operations of bitmaps with its Alpha Blend unit

- Draws lines, polygons, circles using its hardware efficient & pixel accurate Bresenham Algorithm Line Drawing Unit

-

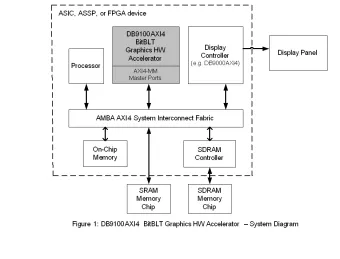

BitBLT Graphics Hardware Accelerator (AXI4 Bus)

- Bit Block Transfer – 3 Independent Memory Sources of data:

- 2D Raster Operations (ROP) performed on Block Transfers:

- BitBLT Draw Features:

- 2D Graphics Rendering Engine (Option):

-

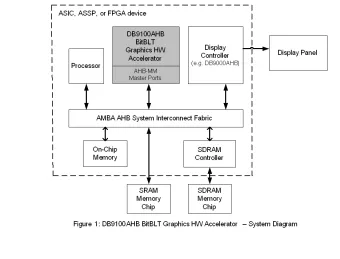

BitBLT Graphics Hardware Accelerator (AHB Bus)

- The DB9100AHB BitBLT Graphics Hardware Accelerator Verilog IP Core renders a graphics frame by generating new bitmaps from commands to combining existing bitmaps on and off-screen using one of 256 Raster Operations.

- A Raster Operation (ROP) is a bitwise Boolean operation (such as AND, OR, XOR, NOT).

- The DB9100AHB also contains a Monochrome Bitmap Color Expansion feature, typically used for font expansion of compressed character bitmaps.

- A 1-bit depth bitmap is expanded to one of two colors, a foreground or background color, with the foreground color representing the text, and the background color the non-text background.

-

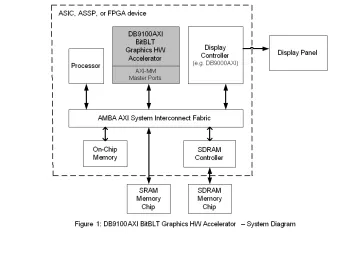

BitBLT Graphics Hardware Accelerator (AXI Bus)

- The DB9100AXI BitBLT Graphics Hardware Accelerator Verilog IP Core renders a graphics frame by generating new bitmaps from commands to combining existing bitmaps on and off-screen using one of 256 Raster Operations.

- A Raster Operation (ROP) is a bitwise Boolean operation (such as AND, OR, XOR, NOT).

- The DB9100AXI also contains a Monochrome Bitmap Color Expansion feature, typically used for font expansion of compressed character bitmaps. A 1-bit depth bitmap is expanded to one of two colors, a foreground or background color, with the foreground color representing the text, and the background color the non-text background.

-

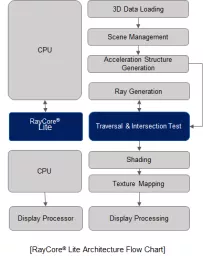

Path tracing/Ray tracing accelerator

- Powerful Path Tracing Acceleration GPU IP Solution

- ‘Unified’ Traversal and Intersection Test

- Based on High Performance MIMD Architecture

- Highly Applicable for Servers and High End GPU Chips