GEM NFC IP

Filter

Compare

26

IP

from

10

vendors

(1

-

10)

-

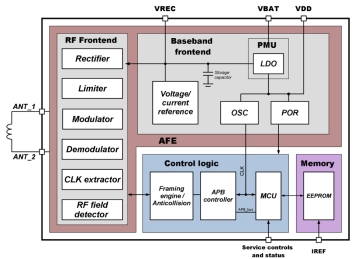

NFC wireless interface supporting ISO14443 A and B with EEPROM on SMIC 180nm

- The IP block provides the physical layer implementation of ISO 14443 interface. In particular, it includes the necessary functional devices for receiving data on the connected antenna, for the response load modulation, received and transmitted data (de)framing and parallel interface to external CPU.

- This IP also can be used for adding NFC functionality to mobile devices and other applications to perform high-level RFID protocol tasks.

-

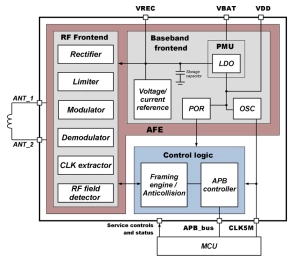

NFC wireless interface supporting ISO14443 A and B on SMIC 180nm

- The IP block provides the physical layer implementation of ISO 14443 interface. In particular, it includes the necessary functional devices for receiving data on the connected antenna, for the response load modulation, received and transmitted data (de)framing and parallel interface to external CPU.

- This IP also can be used for adding NFC functionality to mobile devices and other applications to perform high-level RFID protocol tasks.

-

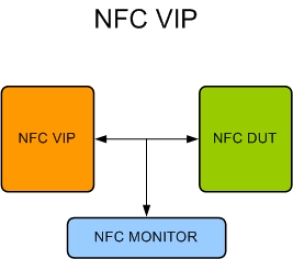

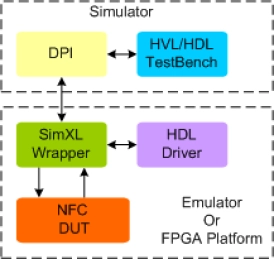

NFC Verification IP

- Compliant with NFC Specification ISO/IEC 18092, ISO/IEC 14443, ISO/IEC 15693, NFC Forum and ECMA 340 standards.

- Complete NFC PCD/PICC functionality.

- Support Half Duplex of operations.

- Supports all the four data rates.

-

NFC Synthesizable Transactor

- Compliant with NFC Specification ISO/IEC 18092, ISO/IEC 14443, ISO/IEC 15693 and ECMA 340 standards

- Complete NFC PCD/PICC functionality

- Supports Half Duplex of operations

- Supports all the four data rates

-

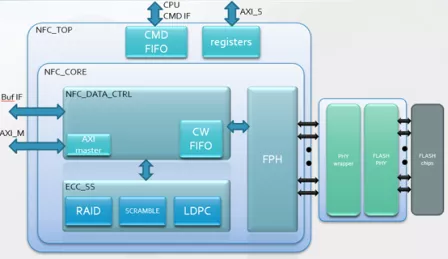

NAND Flash Controller

- The NFC IP is a NAND Flash Controller for accessing user data from NAND Flash chips.

- It is designed with scalability in mind and provides standard AXI interface for the ease of integration in SoC design.

- The NFC has many configurable features to support the requirements for different NAND Flash applications.

-

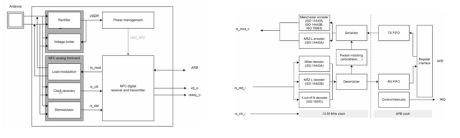

NFC (PICC, UHF, Controller) IP

- NFC PICC Front-End IP - ISO/IEC 14443-A/B compliant: Data rates from 106kbps to 848kbps

- ISO/IEC 15693 compliant: PICC to PCD: one and two-subcarrier modes: PCD to PICC: 1 of 4, 1 of 256 : ASK modulation from 10% to 100%

- Fully passive (power harvesting by reader chip)

- UHF Front-End IP - Fully EPCGlobal Class 1 Gen2 / ISO18000-6C standards compliant

-

NFC Transceiver

- Differential antenna interfaces with dedicated external capacitors for antenna impedance matching

- Supports ISO14443 A standards in both reader and card emulation mode

- 27.56 MHz Xtal for active mode only

- Support ISO15693 standard in reader mode

-

NFC Tag IP for Proximity Integrated Circuit Cards (PICC) and Vicinity Integrated Circuit Cards (VICC)

- Our state-of-the-art NFC tag IP integrates seamlessly with ISO 14443-A, 14443-B, and 15693 standards.

- Ideal for both battery-less and battery-operated devices, this technology ensures best-in-class performance and versatility.

-

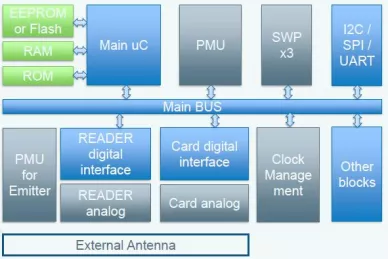

NFC Semiconductor IP - Combo (digital & analog)

- Process: 180nm TSMC or 65nm TSMC(Test version)

- Diesize(incl. pads): 3,000 x 3,000

- Power Consumption: 20 uA(sleep mode), 80mA(active mode)

- CPU: 8051

-

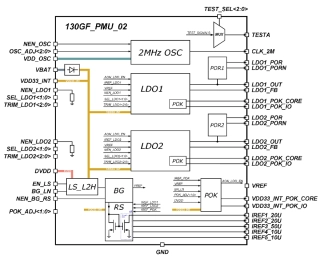

NFC Power Management Unit (0.6/1.2/1.5 V output voltage, 10/20/50 uA output current, 2 MHz output clock frequency)

- 0.6/1.2/1.5 V output voltage, 10/20/50 uA output current, 2 MHz output clock frequency

- GF 130nm Embedded EEPROM technology process

- Reverse current protection