GDDR6 IP

Filter

Compare

29

IP

from

9

vendors

(1

-

10)

-

GDDR6 PHY IP on GF 12nm LPP

- The UniIC GDDR6 PHY,subsequently referred to as the UNIIC_GD6PHY, is designed for performance and power efficiency, its target is to deliver industry-leading data rates of up to 12Gbps/13Gbps/14Gbps and is compatible with JEDEC standard JEDEC250 and DFI 3.1

- The UNIIC_GD6PHY is used to transfer the Command/Address and Datas between the memory controller and the GDDR6 DRAM device; _x000D_ The UNIIC_GD6PHY is available in Global Foundries FinFET 12LPP technology

- The UNIIC_GD6PHY is fully documented and comes with a comprehensive set of deliverables for ease of system modeling and integration.

-

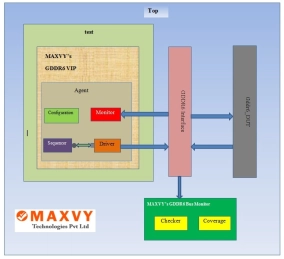

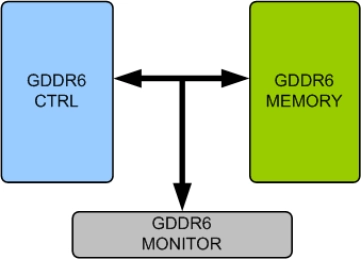

GDDR6 UVM VIP

- The vendor provides configurable GDDR6 verification IP

- GDDR6 is Graphics Double Data Rate 6(GDDR6) which are defined for high-speed interface to access Synchronous Graphics Random Access Memory (SGRAM)

- The VIP provides more flexible configuration for user to select their needs like channel selection,device configuration, write latency, read latency, DDR, QDR data transfer mode

-

Simulation VIP for GDDR6

- Speed

- Supports up to 16Gbps with current vendor datasheets

- Device Density

- Supports a wide range of device densities from 8Gb to 32Gb

-

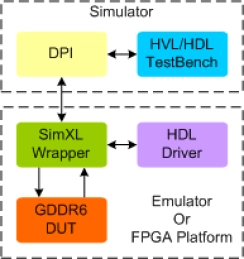

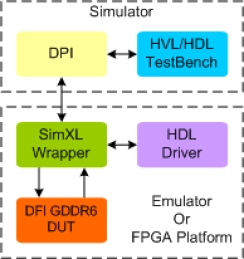

GDDR6 Synthesizable Transactor

- Supports 100% of GDDR6 protocol standard JESD250, JESD250A, JESD250B and JESD250C specification with version 3.12

- Supports all the GDDR6 commands as per the specs

- Supports 2 separate independent channels with point-to-point interface for data, address and command

- Supports double data rate (DDR) or quad data rate (QDR) data

-

GDDR6 DFI Synthesizable Transactor

- Compliant with DFI version 4.0 or 5.0 Specifications.

- Supports GDDR6 devices compliant with JEDEC GDDR6 SGRAM Standard JESD250A and JESD250B.

- Supports GDDR6 x16 or x8 clamshell modes.

- Can be configured as a single controller driving two x16 GDDR6 channels simultaneously (x32 total) or two controllers each driving one x16 GDDR6 channel.

-

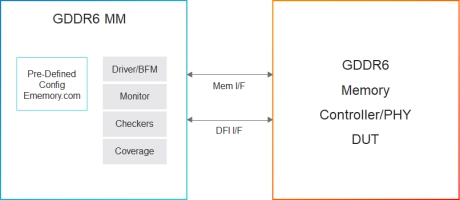

GDDR6 Memory Model

- Supports GDDR6 memory devices from all leading vendors.

- Supports 100% of GDDR6 protocol standard JESD250, JESD250A, JESD250B and JESD250C specification with version 3.12.

- Supports all the GDDR6 commands as per the specs.

- Supports 2 separate independent channels with point-to-point interface for data, address and command.

-

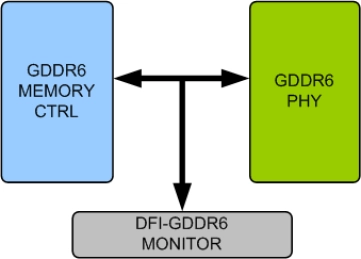

GDDR6 DFI Verification IP

- Compliant with DFI version 4.0 or 5.0 Specifications.

- Supports GDDR6 devices compliant with JEDEC GDDR6 SGRAM Standard JESD250A and JESD250B.

- Supports GDDR6 x16 or x8 clamshell modes.

- Can be configured as a single controller driving two x16 GDDR6 channels simultaneously (x32 total) or two controllers each driving one x16 GDDR6 channel.

-

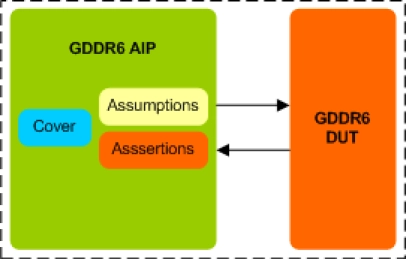

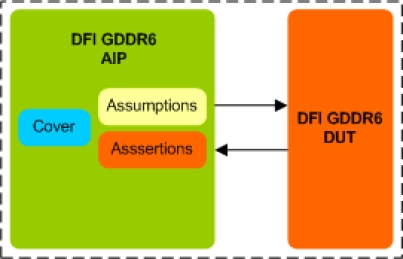

GDDR6 DFI Assertion IP

- Specification Compliance

- Compliant with DFI version 4.0 or 5.0 Specifications.

- Supports GDDR6 devices compliant with JEDEC GDDR6 SGRAM Standard JESD250A and JESD250B.

- Supports GDDR6 x16 or x8 clamshell modes.

-

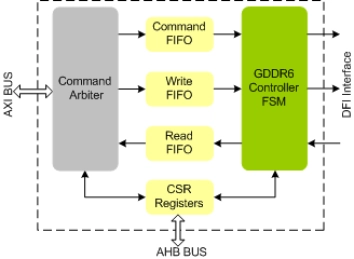

GDDR6 Controller IIP

- Supports GDDR6 protocol standard JESD250, JESD250A and JESD250B specification with version 3.11.

- Compliant with DFI-version 4.0 or 5.0 Specification.

- Supports all the GDDR6 commands as per the specs.

- Supports up to 16 AXI ports with data width upto 512 bits.

-

GDDR6 Assertion IP

- Specification Compliance

- Compliant to ARM GDDR6 protocol

- Supports GDDR6 memory devices from all leading vendors.

- Supports 100% of GDDR6 protocol standard JESD250, JESD250A, JESD250B and JESD250C specification with version 3.12.