Ethernet Packet Processor IP

Filter

Compare

39

IP

from

14

vendors

(1

-

10)

-

Ethernet Switch/Router L2/L3/MPLS 12x10G

- 12 ports of 10 Gigabit Ethernet.

- Full wire-speed on all ports and all Ethernet frame sizes.

- Store and forward shared memory architecture.

- Support for jumbo packets up to 16367 bytes.

-

Ethernet Switch Advanced L2/VLAN 48x1G + 5x10G

- 48 ports of 1 Gigabit Ethernet.

- 5 ports of 10 Gigabit Ethernet.

- Full wire-speed on all ports and all Ethernet frame sizes.

- Store and forward shared memory architecture.

- Support for jumbo packets up to 16359 bytes.

-

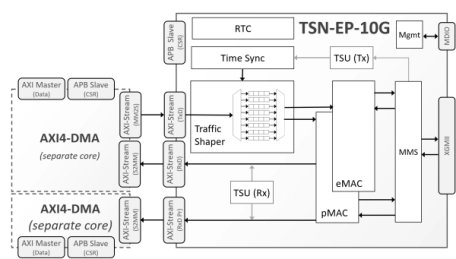

TSN Ethernet Endpoint Controller 10Gbps

- The TSN-EP-10G implements a configurable controller meant to ease the implementation of endpoints for networks complying with the Time Sensitive Networking (TSN) standards

- It integrates hardware stacks for timing synchronization (IEEE 802.1AS-2020) and traffic shaping (IEEE 802.1Qav and 802.1Qbv), frame-preemption (IEEE 802.1Qbu and IEEE 802.3br) and a low-latency Ethernet MAC.

-

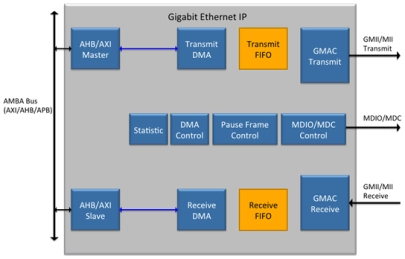

Gigabit Ethernet MAC IP Core

- The silicon-proven Gigabit Ethernet IP core provides a 10/100 Mbps Media Independent Interface (MII) and a 1000 Mbps Gigabit Media Independent Interface (GMII).

- It also supports optional Reduced MII (RGMII), and Serial GMII (SGMII).

-

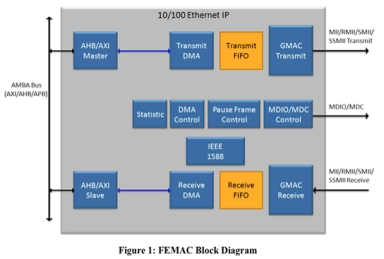

Fast Ethernet Media Access Controller

- The Fast Ethernet Media Access Controller (FEMAC) with AHB or AXI Interface core incorporates the essential protocol requirements for operation of 10/100 Mbps Ethernet/IEEE 802.3-2008 compliant node, and provides interface between the AHB or AXI Interface and the Media Independent Interface (MII) for the Ethernet operation.

- Optionally the core supports RMII (Reduced MII Interface) and SMII (Serial MII Interface) for reducing the pin count to interface with external PHY device.

-

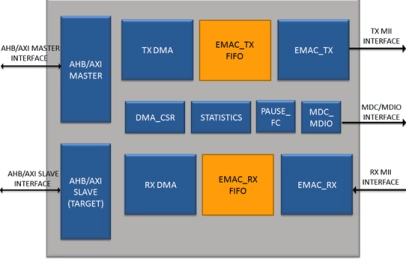

10/100 Ethernet MAC IP core

- The 10/100 Ethernet Media Access Controller (MAC) IP core is compliant with the Ethernet IEEE 802.3-2002 standard and has passed interoperability testing at UNH-IOL.

- The 10/100 Ethernet IP core provides an 10/100 Mbps Media Independent Interface (MII) and an optional processor interface; it also supports Reduced MII (RMII) and Serial MII (SMII).

-

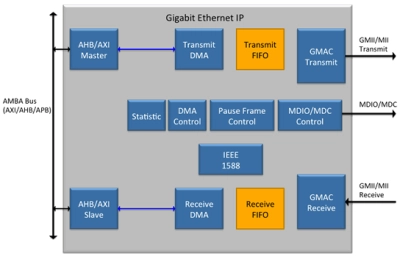

Gigabit Ethernet with IEEE 1588 and AVB

- The Gigabit Ethernet Media Access Controller IP is compliant with the Ethernet IEEE 802.3-2008 standard and supports protocol extensions for Audio Video Bridging (AVB).

- The Gigabit Ethernet IP provides a 10/100 Mbps Media Independent Interface (MII) and a 1000 Mbps Gigabit Media Independent Interface (GMII).

-

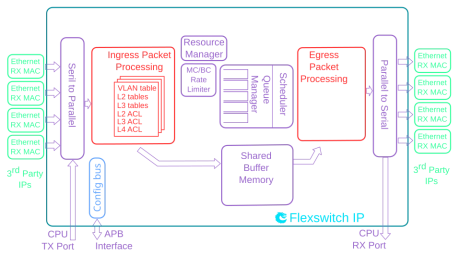

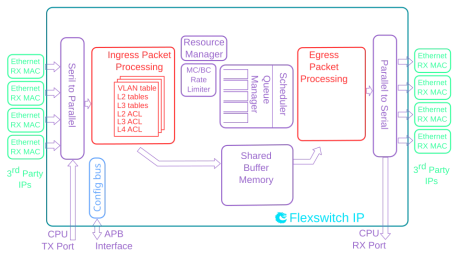

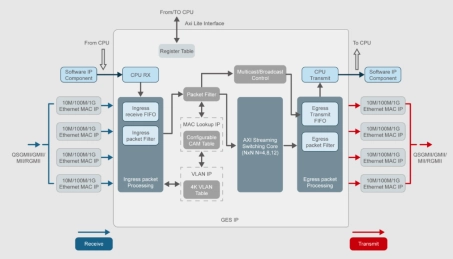

Lithe Layer 2 Gigabit Ethernet Switching IP

- The Lithe Layer 2 Gigabit Ethernet Switching IP is a comprehensive solution for building scalable and efficient network infrastructures.

- Designed to operate at the data link layer of the OSI model, our Lithe Layer 2 IP offers advanced networking capabilities for local area networks (LANs), metropolitan area networks (MANs), and wide area networks (WANs).

- With support for various networking protocols and features, our Lithe IP enables seamless connectivity, reliable data transmission, and efficient network management.

-

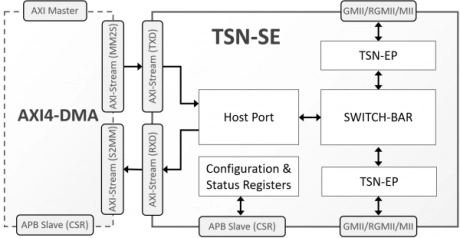

TSN Ethernet Switched Endpoint Controller

- The TSN-SE implements a configurable controller meant to ease the implementation of switched endpoints for Time Sensitive Net-working (TSN) Ethernet networks.

- It integrates hardware stacks for timing synchronization (IEEE 802.1AS-2020), traffic shaping (IEEE 802.1Qav and IEEE 802.1Qbv), frame-preemption (IEEE 802.1Qbu and IEEE 802.3br) and a low-latency Ethernet MAC.

-

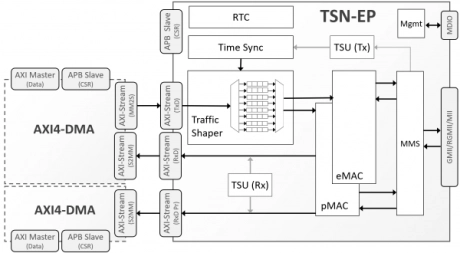

TSN Ethernet Endpoint Controller

- The TSN-EP implements a configurable controller meant to ease the implementation of endpoints for networks complying to the Time Sensitive Networking (TSN) standards.

- It integrates hardware stacks for timing synchronization (IEEE 802.1AS-2020) and traffic shaping (IEEE 802.1Qav and 802.1Qbv), frame-preemption (IEEE 802.1Qbu and IEEE 802.3br) and a low-latency Ethernet MAC.