Ethernet IP

Filter

Compare

836

IP

from

100

vendors

(1

-

10)

-

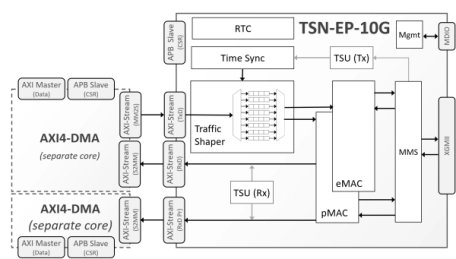

TSN Ethernet Endpoint Controller 10Gbps

- The TSN-EP-10G implements a configurable controller meant to ease the implementation of endpoints for networks complying with the Time Sensitive Networking (TSN) standards

- It integrates hardware stacks for timing synchronization (IEEE 802.1AS-2020) and traffic shaping (IEEE 802.1Qav and 802.1Qbv), frame-preemption (IEEE 802.1Qbu and IEEE 802.3br) and a low-latency Ethernet MAC.

-

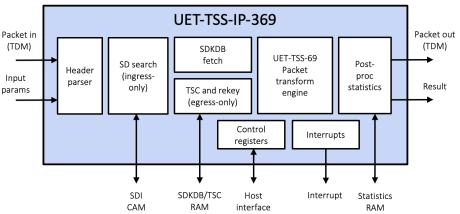

Multi-channel Ultra Ethernet TSS Complete Layer

- The UET-TSS-IP-369 (EIP-369) is an inline, high-performance, multi-channel packet engine that provides the complete TSS layer, bypass/drop and basic crypto processing at rates up to 1.6Tbps.

- The engine is designed for integration into the systems that require TSS processing for one or more ports. The engine is provided as separate ingress and egress data paths.

- The EIP-369 embeds the UET-TSS-IP-69 for the packet transformation.

-

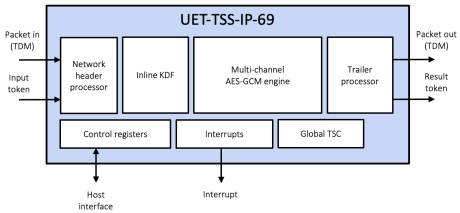

Multi-channel Ultra Ethernet TSS Transform Engine

- The UET-TSS-IP-69 (EIP-69) is a high-performance, multi-channel transform engine that provides the complete TSS packet transformation (including KDF and IP/UDP updates), bypass/drop and basic crypto processing at rates up to 1.6Tbps.

- The engine is designed for integration into the systems that require TSS processing for one or more ports. The engine is provided as separate ingress and egress data paths.

-

HPC MACsec Security Modules for Ethernet

- IEEE 802.1ae, IEEE 802.1br Support

- 100 Gbps—1.6 Tbps

- Can reach higher throughputs scalable to 3.2 Tbps

- Supports also lower performance modes down to 10 Gbps

-

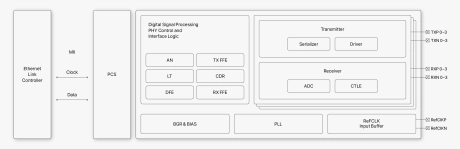

Ethernet PHY IP

- Compliant to 802.3 Ethernet specification - 200GBASE-KR4, 200GBASE-CR4, 100GBASE-KR4, 100GBASE-CR4, 100GBASE-KR2, 100GBASE-CR2, 50GBASE-KR, 50GBASE-CR, 40GBASE-KR4, 40GBASE-CR4, 25GBASE-KR, 25GBASE-CR, 10GBASE-KR, 10GBASE-CR

- Data rate supported - Ethernet: NRZ 3.125 - 26.5625Gb/s, PAM4 53.125Gb/s

- DSP-based architecture using high-performance ADC/DAC for RX/TX

-

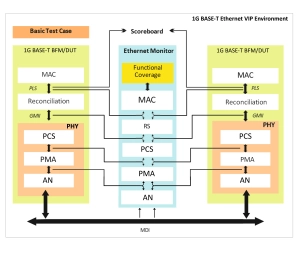

1G BASE-T Ethernet Verification IP

- The 1G BASE-T Ethernet Verification IP provides deliverables an effective & efficient way to verify the components interfacing with the Ethernet interface of an IP or SoC.

- The 1G Ethernet VIP is fully compliant with the IEEE standard 802.3 specification.

- This VIP is lightweight with easy plug -and- play interface so that there is no hit on the design cycle time.

-

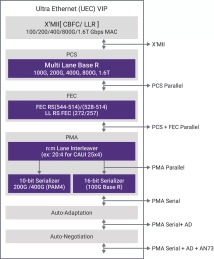

Simulation VIP for Ethernet UEC

- Support testbench language interfaces for SystemVerilog, UVM, OVM, e, and SystemC

- Callbacks access at multiple TX and RX queue points for scoreboarding, data manipulation, and error injection

- Transaction Tracker: Configurable tracking of all the transactions on the channels

-

Gigabit Ethernet Controller

- XEC is a high performance 1000M/100M/10M Ethernet Controller IP. It support GMII/RGMII/MII/RMII MAC-PHY interface and support AXI/AHB system bus.

- XEC can receive the data from Ethernet PHY to the AXI/AHB bus, and to send out data from AXI/AHB bus to the Ethernet PHY.

-

Verification IP for Ultra Ethernet (UEC)

- Native SystemVerilog/UVM

- Source code test suite including UNH-IOL (optional)

- Runs natively on major simulators

- Built-in protocol checks

- Verification plan and coverage

-

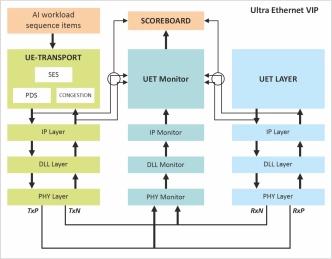

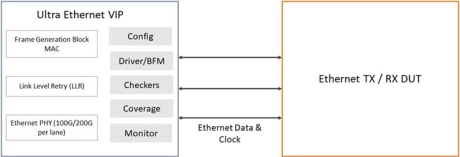

Ultra Ethernet Verification IP

- The Ultra Ethernet (UE) Verification IP provides an effective & efficient way to verify the components interfacing with Ethernet interface of an IP or SoC.

- The UE VIP is compliant with IEEE standard 802.3-2018 & UE Specifications V1.0.

- This VIP is light weight with easy plug-and-play interface so that there is no hit on the design cycle time.