Display Port/eDisplay Port IP

Filter

Compare

643

IP

from

66

vendors

(1

-

10)

-

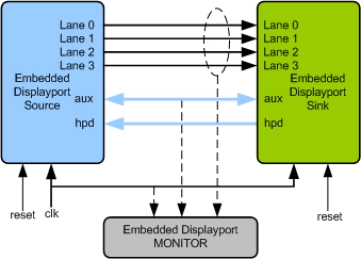

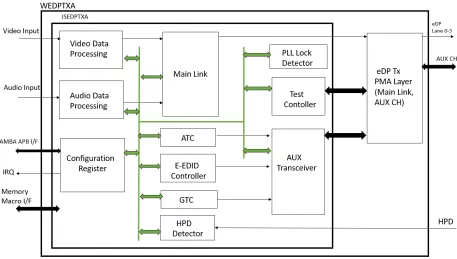

Embedded Display Port Verification IP

- Full Embedded Display port source device and sink device functionality.

- Embedded Display port v1.3,1.4,1.4b and 1.5 compliant and based on display port specs 1.2/1.2a/1.3/1.4/2.0.

- Support transmitter and receiver Mode.

- Supports multi lanes upto 4 lanes.

-

Display Port 2.0 Verification IP

- Full Display port 2.0 source device and sink device functionality.

- Supports backward compatibility with previous versions upto DPv1.4a

- Supports multi lanes upto 4 lanes.

- Supports control symbols for framing.

-

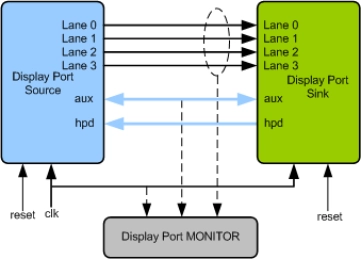

Display Port Verification IP

- Full Display port source device and sink device functionality.

- Display port supports version 1.0,1.1,1.2,1.2a,1.3,1.4,1.4a and 2.0 specification.

- Supports multi lanes upto 4 lanes.

- Supports control symbols for framing(Both Default & Enhanced framing mode).

-

Display Port Synthesizable Transactor

- Supports full Display port source device and sink device functionality

- Supports multi lanes upto 4 lanes

- Supports control symbols for framing(Both Default & Enhanced framing mode)

- Supports interlaced & non-interlaced video stream

-

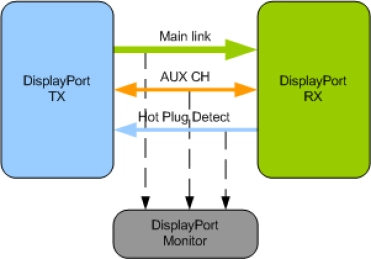

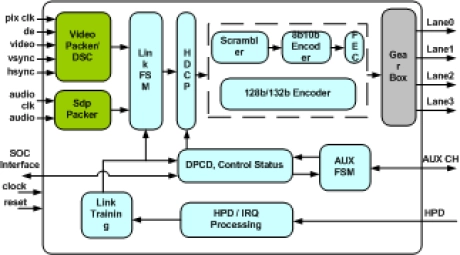

DISPLAY PORT TRANSMITTER IIP

- Compliant with Display Port version 2.0 specification.

- Supports full Display port Transmitter functionality

- Supports multi lanes upto 4 lanes

- Supports 10bit, 20bit, 40bit and 80bit parallel interfaces

-

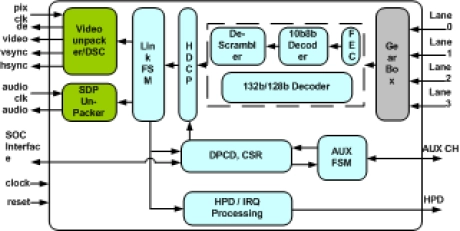

DISPLAY PORT RECEIVER IIP

- Compliant with Display Port version 2.0 specification.

- Supports full Display port Receiver functionality

- Supports multi lanes upto 4 lanes

- Supports 10bit, 20bit, 40bit, and 80bit parallel interfaces

-

Display Port v1.4 Rx PHY & Controller IP, Silicon Proven in UMC 55SP

- DisplayPort version 1.4 compliant receiver

- PHY supports 1.62Gbps (RBR) to 5.4Gbps (HBR2) bit rate

- Integrated 100-ohm termination resistors with common-mode biasing

- Integrated equalizer with tunable strength

-

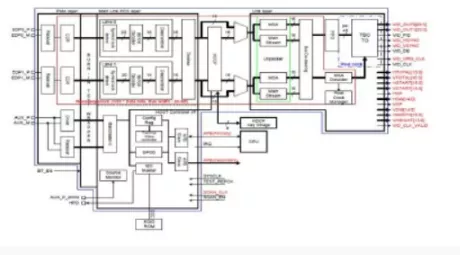

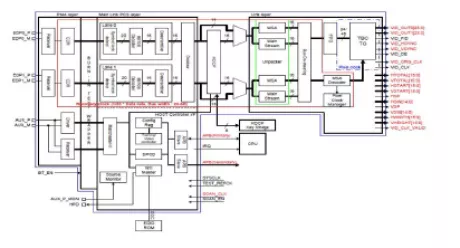

Display Port v1.4 Tx PHY & Controller IP, Silicon Proven in TSMC 12FFC

- eDP version 1.4a / DP version 1.4 compliant transmitter

- Supports HDCP1.4 and HDCP2.2(Optional)

- Supports Forward Error Correction (Optional)

- Consists of configurable (4/2/1) link channels and one AUX channel

-

Display Port 1.4 Rx PHY & Controller IP (Silicon Proven in IDM 180nm /150nm)

- DisplayPort version 1.4 compliant receiver

- PHY supports 1.62Gbps (RBR) to 5.4Gbps (HBR2) bit rate

- Integrated 100-ohm termination resistors with common-mode biasing

- Integrated equalizer with tunable strength

-

Display Port v1.4 Rx PHY & Controller IP, Silicon Proven in UMC 40SP

- DisplayPort version 1.4 compliant receiver

- PHY supports 1.62Gbps (RBR) to 5.4Gbps (HBR2) bit rate

- Integrated 100-ohm termination resistors with common-mode biasing

- Integrated equalizer with tunable strength