DVB-S2 IP

Filter

Compare

50

IP

from

13

vendors

(1

-

10)

-

DVB-S2 LDPC BCH Decoder and Encoder

- The DVB-S2 LDPC-BCH block is a powerful FEC (Forward Error Correction) subsystem for Digital Video Broadcasting via Satellite.

- In Digital video broadcasting for digital transmission for satellite applications, a powerful FEC sub-system is needed. FEC is based on LDPC (Low Density Parity Check) codes concatenated with BCH (Bose Chaudhuri Hocquenghem) codes, allowing Quasi Error Free operation close to the Shannon limit.

-

DVB-S2 Modulator

- Fully synchronous design, using single clock

- Fully synthesizable drop-in module for FPGAs

- Optimized for high performance and low resources

- Low implementation loss

-

DVB-S2 Demodulator

- Compliant with ETSI 302 307 V1.2.1 (2009-08) (DVB-S2)

- Supports CCM mode for broadcasting. ACM and VCM modes will be available soon

- Support for QPSK and 8-PSK modulations. 16-APSK and 32-APSK will be available soon

- Support for short blocks (16200 bits) and long blocks (64800 bits)

-

LDPC Decoder and Encoder that supports DVB-S2 DVB-S2X DVB-T2 DVB-C2 CMMB DMB-T

- LDPC decoder and encoder that supports several standards:

- Versions available for different throughput, up to several Gbps.

- Unique architecture assures easy place and rout.

-

DVB-S2 BCH and LDPC Encoder and Decoder

- Compliant with ETSI 302 307 V1.2.1 (2009-08) (DVB-S2).

- Support for short blocks (16200 bits) and long blocks (64800 bits).

- Support for all modulation schemes (QPSK, 8-PSK, 16-APSK, 32-APSK).

- Support for all interleaving schemes of all modulation schemes.

-

DVB-S2 Modulator

- ASI interface for incoming TS-packets

- Supports QPSK, 8PSK, 16APSK & 32APSK modulation

- Supports VCM operation

- Normal and short frame sizes

-

DVB-S2 Demodulator

- Excellent performance

- Supports QPSK, 8PSK, 16APSK & 32APSK modulations

- Supports VCM operation

- Normal and short frame sizes

-

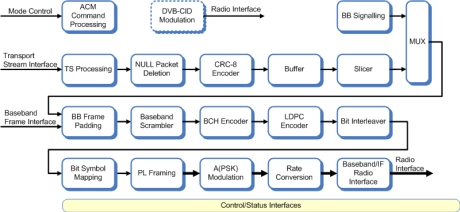

DVB-S2 modulator

- The CMS0025 DVB-S2/S2X Modulator with integrated LDPC encoder has been designed specifically to address the requirements of the ETSI DVB-S2 forward-link satellite standard (EN 302 307), section-1 together with the section-2 extensions (DVB-S2X), with additional support for DVB-S2X VLSNR operation. The core can operate in CCM and VCM/ACM modes.

- The core provides all the necessary processing steps to modulate a single transport stream (or baseband frame) into a complex I/Q signal for input to a pair of DACs, or an interpolating DAC device such as the AD9857(or AD9957). Optionally, the output can be selected as an IF to supply a signal DAC.

-

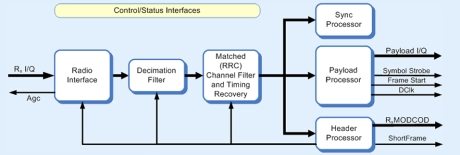

DVB-S2 (A)PSK Demodulator

- The CMS0014 DVB-S2 (A)PSK Demodulator is a high-performance (A)PSK demodulator core intended for DVB-S2 and DVB-S2X forward link applications.

- The demodulator is compatible with the ACM, VCM and CCM configurations of the DVB-S2 Standard including DVB-S2 extensions and is therefore suitable for the reception of DVB broadcast, DSNG, professional and broadband interactive services.

-

DVB-S2 Demodulator

- DVBS2_DEMOD.vhd performs the demodulation based on three tracking loops: carrier tracking (for coherent demodulation), symbol timing tracking, and AGC.

- Each output bit’s quality is expressed as Log-Likelihood Ratio (LLR) for use.

- The receiver operates in two clock domains: global clock CLKRXg (half the ADC sampling rate) is mostly for demodulation.