DDRn Memory Controller IP

Filter

Compare

385

IP

from

48

vendors

(1

-

10)

-

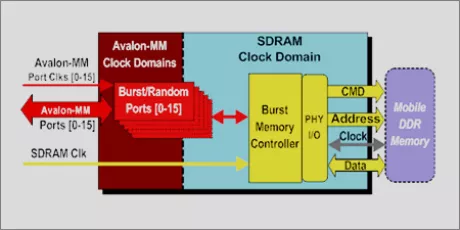

Avalon Mobile DDR Memory Controller

- 200 MHz Cyclone / Stratix memory performance

- Supports all standard Mobile DDR SDRAM devices

- 1 to 16 Avalon® independent local bus port interfaces

- Avalon Pipelined and Burst transfers

-

DO-254 DDR Memory Controller 1.00a

- DDR, DDR2, DDR3, and LPDDR (Mobile DDR) memory standards support

- Up to 800 Mb/s (400 MHz double data rate) performance

- Up to four MCB cores in a single Spartan-6 device

- Configurable dedicated multi-port user interface to FPGA logic

-

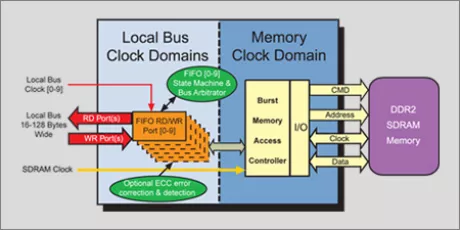

Avalon Multi-port DDR2 Memory Controller

- 200 / 333 MHz (400/666 Mbps) Cyclone/Stratix DDR2 memory performance

- DDR2 Memory Devices

- From 1 to 16 Avalon-MM local bus port interfaces

- Memory bandwidth utilization in excess of 95%

-

-

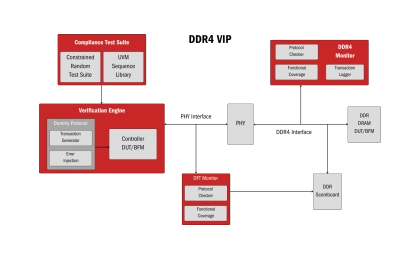

DDR4 Controller - Validates memory compliance, optimizes performance, ensures reliability

- The DDR4 Memory Controller Verification IP ensures compliance with DDR4 standards, validating high-speed data transfer, read/write operations, and error correction. It provides automated testing, advanced debugging tools, and scalability for complex memory systems.

- Designed for versatile applications, this IP optimizes performance in gaming consoles, data centers, AI systems, networking devices, and more. It ensures memory reliability, efficiency, and scalability across industries, accelerating time-to-market for DDR4-based products

-

DDR5 Memory Controller IP with Advanced Feautures

- Supports DDR5 protocol standard JESD79-5 Specification.

- Compliant with DFI version 5.0 Specification.

- Supports up to 16 AXI ports with data width upto 512 bits.

- Supports controllable outstanding transactions for AXI write and read channels

-

DDR4 Memory Controller IP with high performance

- Supports DDR4 protocol standard JESD79-4, JESD79- 4A, JESD79-4A_r2, JESD79-4B, JESD79-4C and JESD79-4D (Draft) Specification.

- Compliant with DFI-version 3.0 or higher Specification.

- Supports up to 16 AXI ports with data width upto 512 bits.

- Supports controllable outstanding transactions for AXI write and read channels

-

DDR Memory Controller IP for low power and high reliability

- Supports DDR protocol standard JESD79F Specification.

- Compliant with DFI-version 2.0 or higher Specification.

- Supports all the DDR commands as per the specs. Supports up to 16 AXI ports with data width upto 512 bits.

- Supports controllable outstanding transactions for AXI write and read channels

-

DDR3 SDRAM Memory Controller

- Supports DDR3 SDRAM memory devices on AMD-Xilinx 7 Series FPGAs

- Size optimized – ideal for low cost 7 Series FPGAs (Artix-7, Spartan-7)

-

High Performance DDR 3/2 Memory Controller IP

- Supports DDR3/DDR2 SDRAM

- 16 bits width DDR2/DDR3 SDRAM Interface

- Memory Clock up to 462MHz, DFI Clock up to 462MHz

- Support DDR2 667/800/1066 and DDR3 667/800/1066/1333/1600/1866