DDR5 MRDIMM IP

Filter

Compare

5

IP

from

3

vendors

(1

-

5)

-

DDR5 MRDIMM PHY and Controller

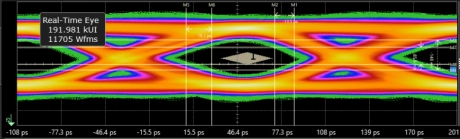

- The DDR5 12.8Gbps MRDIMM Gen2 PHY and controller memory IP system solutions double the performance of DDR5 DRAM.

- The DDDR5 12.8Gbps design and architecture address the need for greater memory bandwidth to accommodate unprecedented AI processing demands in enterprise and data center applications, including AI in the cloud.

-

MRDIMM DDR5 & DDR5/4 PHY & Controller

- The DDR IP Mixed-Signal MRDIMM DDR5 PHY and DDR5/4 Combo PHY provide turnkey physical interface solutions for ICs requiring access to JEDEC compatible SDRAM or MRDIMM/ RDIMM/ LRDIMM/ UDIMM DDR5 devices

- It is optimized for low-power and high-speed applications with robust timing and small silicon area

- It supports all JEDEC DDR5/4 SDRAM components in the market

-

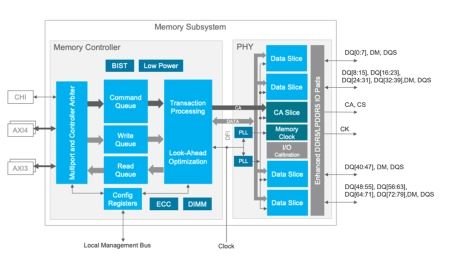

DDR Controller supporting DDR5 MRDIMM Gen2 with Advanced Features Package

- Supports JEDEC standard DDR5 and DDR4 SDRAMs and DIMMs

- Multiport Arm® AMBA® interface (4 AXI™/3 AXI™) with managed QoS or single-port host interface to the DDR controller

- DFI 5.0 compliant interface to Synopsys DDR5/4 PHY or other DDR5/4 PHYs

- Best in class performance with unique features such as QoS-based scheduling and phase-aware scheduling

-

DDR5 MRDIMM2 PHY - TSMC N3P

- Supports JEDEC standard DDR5 and DDR4 SDRAMs

- High-performance DDR PHY supporting data rates up to 8400 Mbps

- PHY independent, firmware-based training using an embedded calibration processor

- Supports up to 4 trained states/ frequencies with <3μs switching time

-

DDR5 MRDIMM2 PHY - TSMC N2P

- Supports JEDEC standard DDR5 and DDR4 SDRAMs

- High-performance DDR PHY supporting data rates up to 8400 Mbps

- PHY independent, firmware-based training using an embedded calibration processor

- Supports up to 4 trained states/ frequencies with <3μs switching time