DC DC regulator IP

Filter

Compare

21

IP

from

11

vendors

(1

-

10)

-

50mA 1.8V Voltage Regulator with Power-Good Signal on XFAB XT018

- The TS_VR_1V8_X8 is a 1.8V linear voltage regulator (LDO) designed to supply the digital core of an ASIC.

- The LDO operates with an input voltage of 3.3V (supply voltage) and provides a regulated output voltage of 1.8V.

- It can provide a maximum DC load current of up to 50mA.

-

10mA 3.3V Low-Dropout (LDO) Regulator on XFAB XT018

- The TS_VR_3V3_X8 is a 3.3V low-dropout linear regulator (LDO) to supply the digital core of an analog ASIC.

- The LDO operates with an input voltage of 5V (supply voltage) and provides an output regulated voltage of 3.3V.

- The LDO can supply a maximum DC load current of 10mA.

-

Linear Regulator, ultra low quiescent current for retention mode TSMC 40uLPeF

- qLR-Aubrey-ref-1.62-3.63-0.55-2.5.02_TSMC_40_uLPeF is an ultra-low quiescent LDO (Linear regulator) in TSMC 40uLPeF.

-

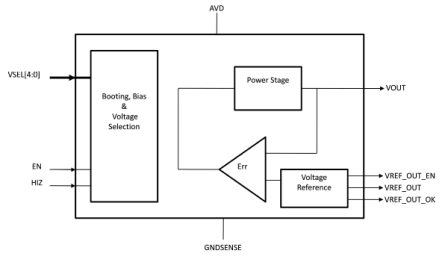

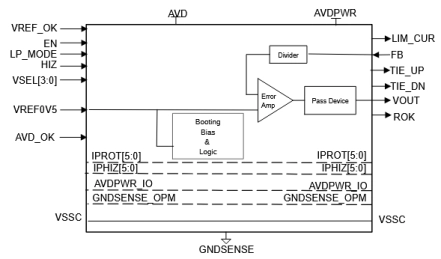

Low input voltage high performance LDO regulator in TSMC 22ULL

- LDO-T22-1-1.8-0.6-1.05_TSMC_22_ULL is a Low input voltage, high performance LDO linear regulator in TSMC 22ULL with programmable output voltage to supply core logic domains, SRAM arrays or RF/analog domains.

- It features normal and low-power (LP) operating modes to adjust the amount of output current depending on the application requirements.

-

LDO regulator on SMIC 40nm, 1.13v output

- The present IP is a low dropout voltage regulator, which can support 10uA DC current load

- The input voltage is 2.7-3.6V (typical: 3.3V)

- Its output voltage range is 0.62V-1.13V-1.75V

- The reference voltage and bias current are 0.6V and 0.5uA from BGR, respectively.

-

LDO regulator on SMIC 40nm, 1.42v output

- The present IP is a low dropout voltage regulator, which can support 10uA DC current load

- The input voltage is 2.7-3.6V (typical: 3.3V)

- Its output voltage range is 0.9V-1.42 V-2.1V

- The reference voltage and bias current are 0.6V and 0.5uA from BGR, respectively.

-

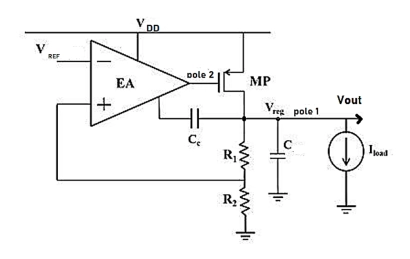

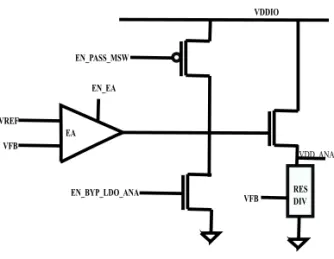

Capless Analog LDO Regulator

- Output current range is 0-15mA.

- Short Circuit Current Limiting and Overtemperature Protection

- Shutdown current< 312nA .

- DC load regulation< 0.99%

-

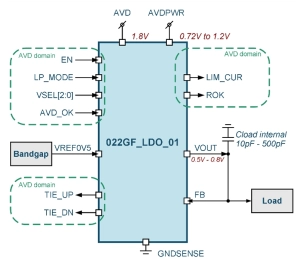

50mA capacitor-less LDO voltage regulator (output voltage 0.5V to 0.8V)

- GF 22nm FDX

- 0.72V – 1.2V input voltage range

- Programmable output voltage from 0.5 to 0.8V

- Normal and LP modes

-

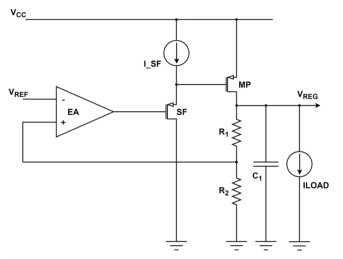

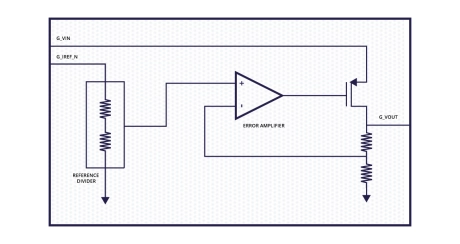

Low Power Regulator

- The agileLDO_LP is a linear regulator, suitable for use in any low power, low current system and is designed to provide a flexible range of regulated output voltages suitable for ultra-low power systems and near-vt operating modes.

- The agileLDO_LP consists of: A voltage reference generator, an error amplifier and a output current source. The regulated output voltage is fed-back into the error amplifier to maintain a constant regulated output over the specified range of input voltages and load currents.

-

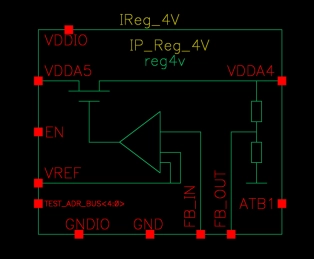

16mA 4V Voltage Regulator on XFAB XT018

- The TS_VR_4V00_X8 is a 4V voltage regulator capable of delivering up to 16mA. It is required for the supply of other TES IPs like TS_FS_9M70_X8,

- TS_VA_LNDC_X8, and TS_CS_20uA_X8. The TS_VR_4V00_X8 operates with one supply voltage, VDDA5, VDDIO (5V typical) and one precision reference voltage VREF (2.5V).