D2D interconnect IP

Filter

Compare

8

IP

from

7

vendors

(1

-

8)

-

D2D Controller addon for D2D SR112G PHY with CXS interface

- Low Latency controller for die-to-die connectivity

- Supports PAM-4 and NRZ PHY signaling mode in all data rates

- Reduces BER with optional FEC configurations

- Supports Arm® AMBA® CXS interface

-

Chiplet Interconnect - Die-to-die interconnect IP solutions for advanced and standard packaging applications

- High data rate of 2–24 Gb/s

- Very low power of < 0.375 pJ/bit @ 2–16 Gb/s 0.5-V VDDQ

- Very low latency of < 2 ns PHY-to-PHY

- Support for 2:1, 4:1, 8:1, 12:1 and 16:1 serialization and deserialization ratios

-

D2D UCIe 1.1

- Compatible with UCIe v1.1 specification

- Features single-ended, source-synchronous, and DDR I/O signaling

- Supports 32-bit (16-bits TX + 16-bit RX) data bus per module for standard packages

- Offers a high clock frequency up to 16GHz

-

D2D UCIe 1.0

- Compatible with UCIe v1.0 specification

- Single-ended, source synchronous and DDR IO Signaling

- Supports 32 bits(16bits TX + 16bits RX) data bus per module for standard package

- High clock frequency, up to 8GHz

-

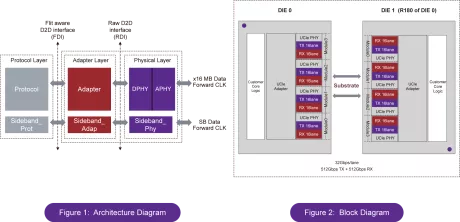

IPTD2D-A PHY and Controller

- Our mass production-proven IPTD2D-A D2D Interconnect IP Solutions offer industry-leading power efficiency, performance, and low latency, tailored for the next generation of high-performance computing, AI, and data center applications.

- With asynchronous “side-band” signals, the IPTD2D PHY can work at any frequency ranging from 2Gbps to 16Gbps, achieving the best balance between total bandwidth and power consumption.

-

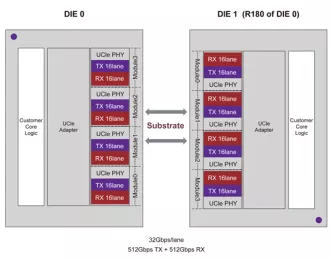

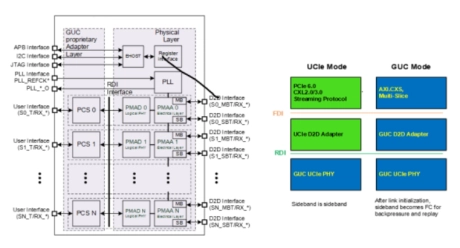

TSMC CLN5FF GUCIe LP Die-to-Die PHY

- IGAD2DY11A is an LP (Low Power) Die-to-Die (D2D) PHY for SoIC-X Face-to-Face advanced package.

- This GUCIe PHY not only supports UCIe specification rev 1.1 compliance physical layer and Raw D2D interface (RDI) but also optionally provides the

-

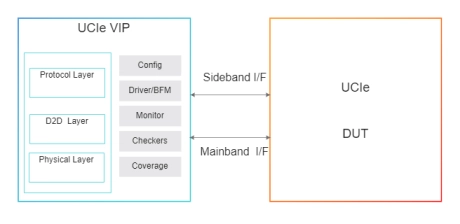

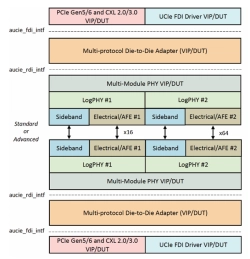

Verification IP for UCIe

- Avery UCIe VIP provides a comprehensive verification solution featuring an advanced UVM environment that incorporates constrained random traffic gener ation, robust D2D and LogPHY layer controls and error injection, protocol checks and coverage, functional coverage, protocol analyzer-like features for debug ging, and performance analysis metrics.

- PCIe/CXL VIP supports FDI/RDI adapters for complete stack verification. With the advanced capabilities of Avery VIP, engineers can work more efficiently, develop more complex tests, and work on more complex topologies, such as bifurcation.

-