Current-Input Analogue Front End IP

Filter

Compare

8

IP

from

1

vendors

(1

-

8)

-

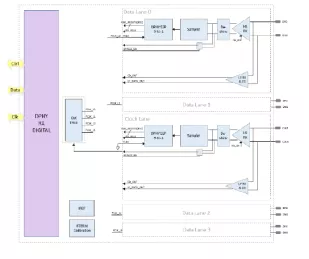

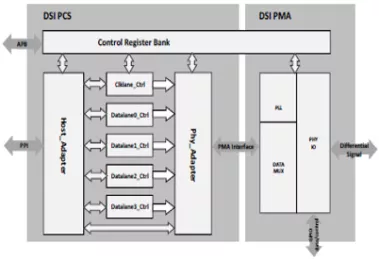

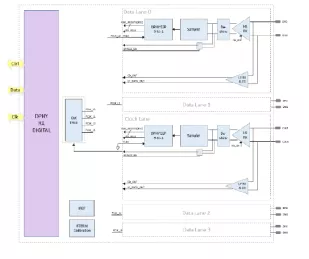

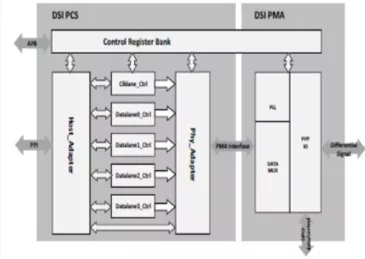

MIPI D-PHY Tx IP, Silicon Proven in GF 55LP

- Compliant to MIPI Alliance Standard for D-PHY specification Version 1.2

- Supports standard PPI interface compliant to MIPI Specification

- Supports synchronous transfer at high-speed mode with a bit rate of 80-2500 Mb/s

- Supports asynchronous transfer at low power mode with a bit rate of 10 Mb/s

-

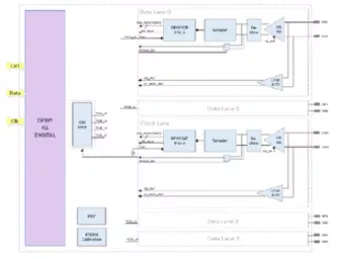

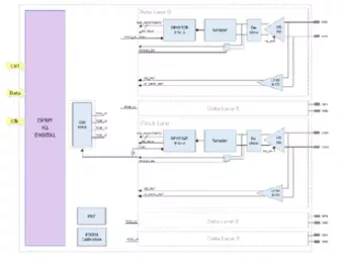

MIPI D-PHY Rx IP, Silicon Proven in TSMC 40LP

- Compliant to MIPI Alliance Standard for D-PHY specification Version 1.2

- Supports standard PPI interface compliant to MIPI Specification

- Supports synchronous transfer at high-speed mode with a bit rate of 80-2500 Mb/s

- Supports asynchronous transfer at low power mode with a bit rate of 10 Mb/s

-

MIPI D-PHY Tx IP, Silicon Proven in TSMC 40LP

- Compliant to MIPI Alliance Standard for

- D-PHY specification Version 1.2

- Supports standard PPI interface compliant to MIPI Specification

- Supports synchronous transfer at high speed mode with a bit rate of 80-2500 Mb/s

-

MIPI D-PHY Tx IP, Silicon Proven in SMIC 55LL

- Compliant to MIPI Alliance Standard for D-PHY specification Version 1.2

- Supports standard PPI interface compliant to MIPI Specification

- Supports synchronous transfer at high-speed mode with a bit rate of 80-2500 Mb/s

- Supports asynchronous transfer at low power mode with a bit rate of 10 Mb/s

-

MIPI D-PHY Rx IP, Silicon Proven in SMIC 55LL

- Compliant to MIPI Alliance Standard for

- D-PHY specification Version 1.2

- Supports standard PPI interface compliant to MIPI Specification

- Supports synchronous transfer at high-speed mode with a bit rate of 80-2500 Mb/s

-

MIPI D-PHY Tx IP, Silicon Proven in UMC 55LP

- Compliant to MIPI Alliance Standard for

- D-PHY specification Version 1.2

- Supports standard PPI interface compliant to MIPI Specification

- Supports synchronous transfer at high-speed mode with a bit rate of 80-2500 Mb/s

-

MIPI D-PHY Rx IP, Silicon Proven in GF 55LP

- Compliant to MIPI Alliance Standard for D-PHY specification Version 1.2

- Supports standard PPI interface compliant to MIPI Specification

- Supports synchronous transfer at high-speed mode with a bit rate of 80-2500 Mb/s

- Supports asynchronous transfer at low power mode with a bit rate of 10 Mb/s

-

MIPI D-PHY Rx IP, Silicon Proven in UMC 55LP

- Compliant to MIPI Alliance Standard for D-PHY specification Version 1.2

- Supports standard PPI interface compliant to MIPI Specification

- Supports synchronous transfer at high-speed mode with a bit rate of 80-2500 Mb/s

- Supports asynchronous transfer at low power mode with a bit rate of 10 Mb/s