Cadence SerDes IP

Filter

Compare

30

IP

from

2

vendors

(1

-

10)

-

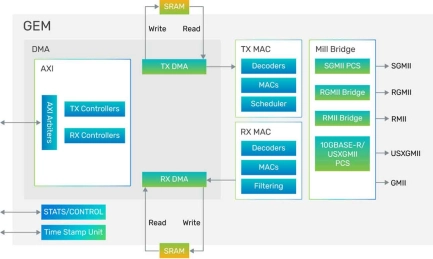

Ethernet PCS IP - Integrates MAC IP to a broad range of PHY and SerDes IP

- Mature: Silicon-proven design in volume production at multiple customers

- Ease-of-use: Customizable with easy integration

- Designed by an Industry Leader: Cadence is an active contributor to the IEEE 802.3 standards working groups

-

112G-ULR PAM4 SerDes PHY

- Supports full-duplex 1.25Gbps to 112.5Gbps data rates

- Superior bit error rate (BER) performance across high-loss and reflective channels

- Compliant with IEEE 802.3ck and OIF standard electrical specifications

- Supports flexible SoC floorplan and IP placement and provides package substrate guideline/reference designs

-

56G-LR Pam4 SerDes PHY

- Supports Ethernet, FC, CPRI, and eCPRI protocols

- Compliant to IEEE 802.3ck and OIF standard electrical specifications

- Supports 56Gbps PAM4 and 28G, 10G, and sub-10Gbps NRZ data rates

- Unique firmware-controlled adaptive power design provides optimal power and performance tradeoffs and more efficient system designs based on platform requirements

- Continuous calibration and adaption provide robust performance across process, voltage, and temperature

- Supports industrial temperature range -40°C – 125°C

-

112G-ELR PAM4 SerDes PHY - TSMC 5nm

- TSMC 5nm FinFET CMOS Process

- Power-optimized for ELR and LR links

- Integrated BIST capable of producing and checking PRBS

- 56-112Gbps PAM4 or 1-56Gbps NRZ data rates

-

PCIe 4/3/2 SerDes PHY - GLOBALFOUNDRIES 22nm

- Duplex lane configurations of x2, x4, and x35

- Transmit swing of at least 800mV differential peak-to-peak for MR & LR, 360mv for SR

- Support for AC-coupled interfaces

- Fine-grain power up/down capability for power optimization, and ability to turn off unused link(s)

-

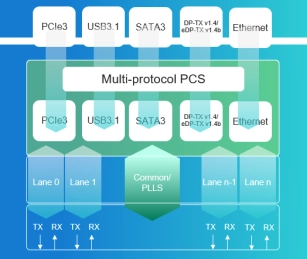

28G LR Multi-Protocol SerDes (MPS) PHY - Samsung 14nm

- Optimized for low-power operation and north/south die-edge placement

- Duplex Lane configurations of x4 and x1

-

28G LR Multi-Protocol SerDes (MPS) PHY - GLOBALFOUNDRIES 12nm

- Optimized for low-power operation and north/south die-edge placement

- Duplex Lane configurations of x4 and x1

-

32G LR Multi-Protocol SerDes (MPS) PHY - GLOBALFOUNDRIES 22nm

- Supports data rates of 2.5 to 32 Gbps

- Optimized for low-power operation and north/south die-edge placement

- AC-coupled RX front end with on-chip capacitors

- Flexible ASIC interface for sharing impedance codes among multiple PMA hard macros and reducing the number of external reference resistors for impedance calibration

-

Ethernet SerDes - 16Gbps and 10Gbps multi-protocol SerDes PHY

- Wide range of protocols that support networking, HPC, and applications

- Low-latency, long-reach, and low-power modes

- Multi-Link PHY—mix protocols within the same macro

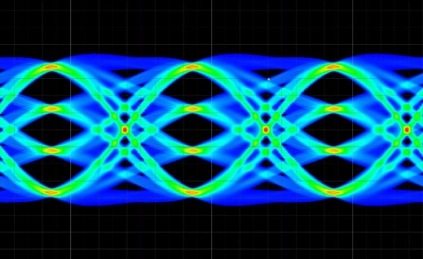

- EyeSurf —non-destructive on-chip oscilloscope

- Extensive set of isolation, test modes, and loop-backs including APB and JTAG

- Supports 16-bit, 20-bit, and 32-bit PIPE and non-PIPE interfaces

- Selectable serial pin polarity reversal for both transmit and receive paths

-

224G SerDes PHY and controller for UALink for AI systems

- UALink, the standard for AI accelerator interconnects, facilitates this scalability by providing low-latency, high-bandwidth communication.

- As a member of the UALink Consortium, Cadence offers verified UALink IP subsystems, including controllers and silicon-proven PHYs, optimized for robust performance in both short and long-reach applications and delivering industry-leading power, performance, and area (PPA).