Cache Coherent Interconnect IP

Filter

Compare

127

IP

from

7

vendors

(1

-

10)

-

Coherent Mesh Network

- High-Performance, Scalable Coherent Mesh

- Reduce SoC Integration Time

- Maximize Compute Density

- Coherent Multichip Links

-

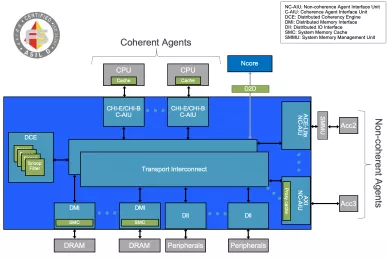

Ncore 3 Coherent Network-on-Chip (NoC)

- Supports multiple coherent agents, including Armv9 and RISC-V CPU clusters

- AMBA CHI-E, CHI-B and ACE interoperability, as well as ACE-Lite and AXI

- Low-latency proxy caches for efficient and quick integration of hardware accelerators into the coherent domain

- Configurable last-level caches

-

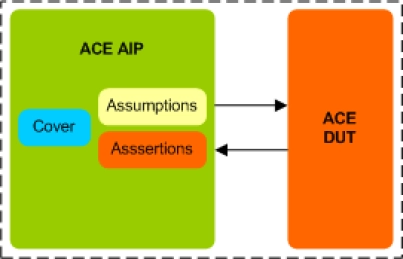

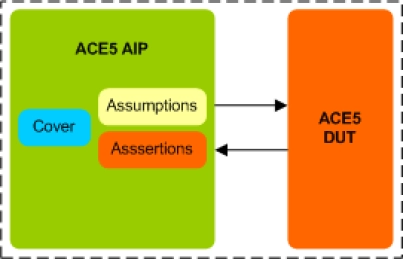

AMBA ACE4 Assertion IP

- Specification Compliance

- Compliant with the latest ARM AMBA ACE4 Protocol Specification.

- Supports all ACE4 data and address widths.

- Supports all protocol transfer types, burst types, burst lengths, burst sizes and response types.

-

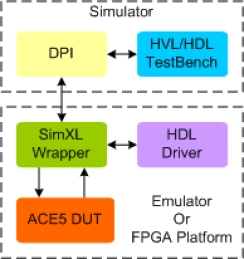

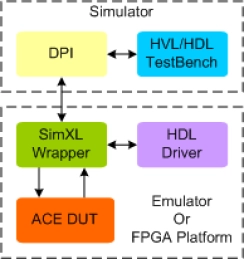

AMBA ACE5 Synthesizable Transactor

- Compliant with the latest ARM AMBA ACE5 Protocol Specification.

- Supports ACE5 Master and Slave.

- Supports all ACE5 data and address widths.

- Supports all protocol transfer types, burst types, burst lengths and response types.

-

AMBA ACE4 Synthesizable Transactor

- Compliant with the latest ARM AMBA ACE4 Protocol Specification.

- Supports ACE4 Master and Slave.

- Supports all ACE4 data and address widths.

- Supports all protocol transfer types, burst types, burst lengths, burst sizes and response types.

-

AMBA ACE5 Assertion IP

- Specification Compliance

- Compliant with the latest ARM AMBA ACE5 Protocol Specification.

- Supports all ACE5 data and address widths.

- Supports all protocol transfer types, burst types, burst lengths and response types.

-

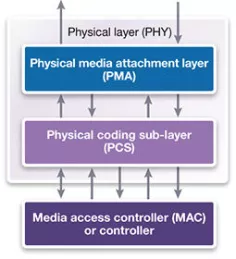

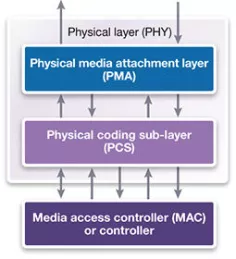

25G PHY, TSMC N6 x2 North/South (vertical) poly orientation

- Supports 1.25 to 25.8 Gbps data-rate

- Supports PCI Express 4.0 with lane margining, 1G to 100G Ethernet, CCIX, and SATA protocols

- Supports x1 to x16 macro configurations with aggregation and bifurcation

- Spread Spectrum Clock (SSC), ` PCIe Separate Refclk Independent SSC (SRIS) and power management features

-

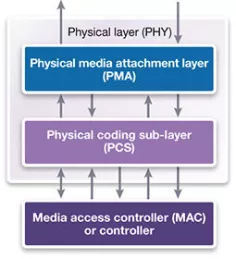

25G PHY, TSMC 7FF x4 North/South (vertical) poly orientation

- Supports 1.25 to 25.8 Gbps data-rate

- Supports PCI Express 4.0 with lane margining, 1G to 100G Ethernet, CCIX, and SATA protocols

- Supports x1 to x16 macro configurations with aggregation and bifurcation

- Spread Spectrum Clock (SSC), ` PCIe Separate Refclk Independent SSC (SRIS) and power management features

-

25G PHY, TSMC 7FF x2 North/South (vertical) poly orientation

- Supports 1.25 to 25.8 Gbps data-rate

- Supports PCI Express 4.0 with lane margining, 1G to 100G Ethernet, CCIX, and SATA protocols

- Supports x1 to x16 macro configurations with aggregation and bifurcation

- Spread Spectrum Clock (SSC), ` PCIe Separate Refclk Independent SSC (SRIS) and power management features

-

25G PHY, TSMC 7FF x1 North/South (vertical) poly orientation

- Supports 1.25 to 25.8 Gbps data-rate

- Supports PCI Express 4.0 with lane margining, 1G to 100G Ethernet, CCIX, and SATA protocols

- Supports x1 to x16 macro configurations with aggregation and bifurcation

- Spread Spectrum Clock (SSC), ` PCIe Separate Refclk Independent SSC (SRIS) and power management features