Analog and Power Management IP

Filter

Compare

160

IP

from

35

vendors

(1

-

10)

-

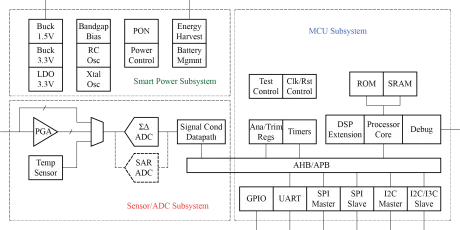

Intelligent Sensor and Power Management Design Platform

- Smart Power Subsystem

- Sensor AFE

- MCU Subsystem

-

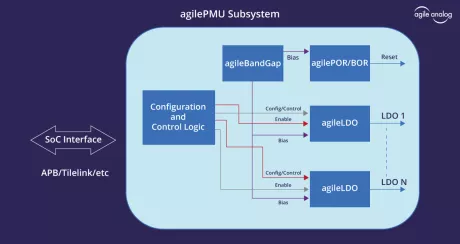

Power Management Subsystem

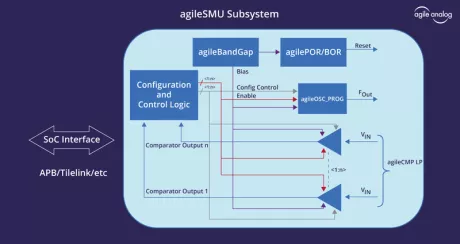

- The agilePMU Subsystem is an efficient and highly integrated Power Management Unit for SoCs/ASICs.

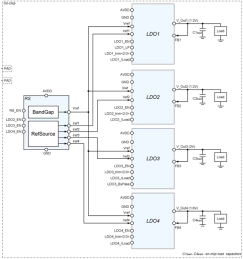

- Featuring a Power-On-Reset (POR), multiple Low Drop-Out (LDO) regulators, and an associated reference generator.

- The agilePMU Subsystem is designed to ensure low power consumption while providing optimal power management capabilities.

-

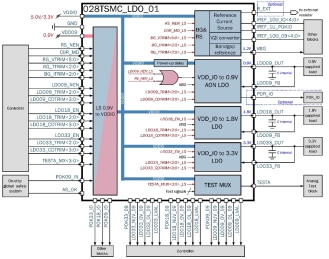

Power management unit (0.9V, 1.8V, 3.3V output voltages, 1.2V reference voltage and 10uA/1uA reference currents)

- TSMC 28nm eFlash technology

- Bandgap output voltage 1.2V

- Bandgap output voltage accuracy without trimming ±3% @5.0V

-

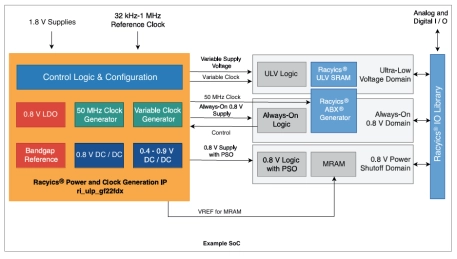

Power and Clock Generation IP - GLOBALFOUNDRIES® 22FDX®

- Tightly integrated power management platform with a soft-IP wrapper around Analog / Mixed-Signal hard macros which generate all supply voltages and clock signals needed to run highly efficient SoCs in GlobalFoundries® 22FDX®.

- Running from only one supply voltage and reference clock, the IP generates its own internal supplies and references, and those needed to run the Racyics® ABX® Generator.

-

Power Management Unit

- UMC 55nm eFlash CMOS technology

- Input Voltage Range: +2.0V to +3.6V

- Four Low Dropout Regulators with output voltage set up

- Output current adjustment

-

RF and Analog GPS/GNSS Front End for GPS, GLONASS, Galileo and Beidu

- Single Channel Mode

- Block Conversion mode

- Configurable 3/4 wire controller

- 2/3 bits A/D detection

-

-

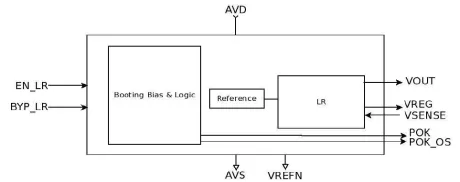

Linear regulator, low-noise optimized for sensitive analog loads such as CODEC and Reference

- Starring a PSRR of -65 dB at 20 kHz and a low intrinsic noise, combined with a low quiescent current of 110 uA, the nLR-VAIPO helps optimize the power management network for audio handheld applications such as smartphone and tablet.

- Small footprint: only 0.12 mm2 (including bandgap reference and POK circuit)

- Minimization of the overall system power, through the support of 3 modes of operation: normal, shutdown and bypass

- Eases integration in SoC nLR-VAIPO is delivered with behavioral models. These new views enable to build an optimized Power Management Network (PMNet) by verifying mode transitions as well as noise propagation.

-

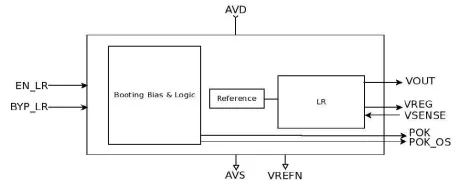

Linear regulator, low-noise optimized for sensitive analog loads such as CODEC and Reference

- Starring a PSRR of -65 dB at 20 kHz and a low intrinsic noise, combined with a low quiescent current of 110 uA, the nLR-VAIPO helps optimize the power management network for audio handheld applications such as smartphone and tablet.

- Small footprint: only 0.12 mm2 (including bandgap reference and POK circuit)

- Minimization of the overall system power, through the support of 3 modes of operation: normal, shutdown and bypass

- Eases integration in SoC nLR-VAIPO is delivered with behavioral models. These new views enable to build an optimized Power Management Network (PMNet) by verifying mode transitions as well as noise propagation.

-

Complete measurement analog front end (AFE) IP for three-phase power metering

- Embedded Computation Engine for utility biling applications

- Low noise Programmable Gain Amplifier (PGA), to reach the best class accuracy with each type of sensors

- Embedded power management for the best resilience to power supply noise