ATSC IP

Filter

Compare

14

IP

from

7

vendors

(1

-

10)

-

4-channel ATSC 8VSB Modulator

- Fully synchronous design, using single clock

- Fully synthesizable drop-in module for FPGAs

-

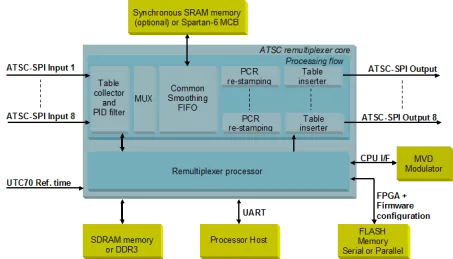

ATSC Remultiplexer N-to-M

- Supported FPGA families: Xilinx Spartan-6, Virtex-6, Artix-7, Kintex-7, Virtex-7, Zynq

- N SPI input / M SPI output (N and M from 1 to 8)

- Adapt one or several MPTS/SPTS stream rate into one or several MPTS by filtering and multiplexing complete services

- Management of PSIP tables (automatic tables generator) according to ATSC A/65:2009, A/53:part 3 and ISO 13818-1.

-

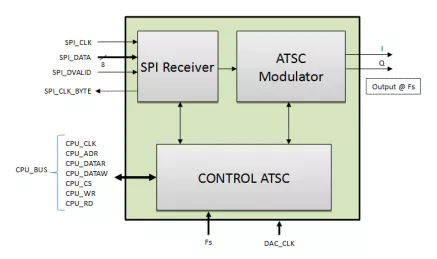

ATSC - 8VSB Modulator

- Drop-in module for Xilinx Spartan-6, Virtex-6, Artix-7, Kintex-7, Virtex-7, Zynq FPGAs

- Single clock (up to 160 MHz)obust SPI input (discarding incorrect input packets)

- PCR re-stamping

- Complex baseband outputs (2 x 16 bits) @ Fsymbol rate

-

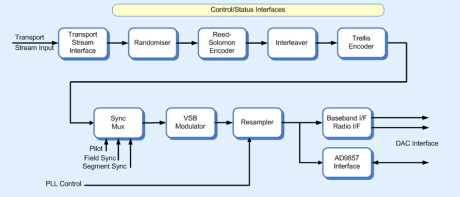

Multi-channel ATSC 8-VSB modulator

- Compliant with ATSC A/53 8-VSB

- Scalable architecture supports 1 to 4 channels per core, and multiple instances per FPGA.

- Variable sample-rate interpolation provides ultra-flexible clocking strategy

- Integrated Reed Solomon/Convolutional channel coder

-

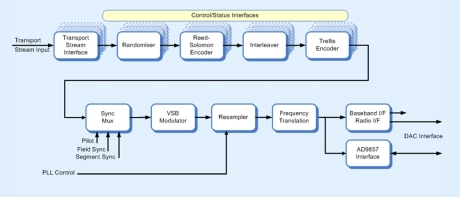

ATSC 8-VSB modulator

- The CMS0033 ATSC 8-VSB Modulator with integrated Channel Coder has been designed specifically to implement the 8-VSB requirements of the ATSC Digital Television Standard (A/53).

- The core provides all the necessary processing steps to modulate a single transport stream into a complex I/Q signal for input to a pair of DACs, or a DDS up-conversion DAC such as the AD9857(or AD9957). Optionally, the output can be selected as an IF to supply a signal DAC.

-

ATSC-M/H Mobile DTV Demodulator

- PHY Layer ATSC M/H (A/153) Demodulation

- Full decoding of TPC and FIC channels

- Autonomous detection and configuration for all M/H signaling modes

- Timeslicing operation for low power applications

-

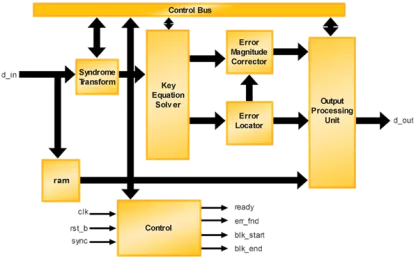

Reed-Solomon Decoder

- Forward Error Correction (FEC) for Communication and Common Applications

- Selectable Reed-Solomon Standards

- Shortened Codes Supported

- Errors/Erasures Supported

-

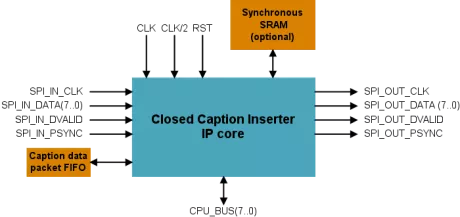

MPEG-TS closed caption inserter

- Supported FPGA families:Xilinx Spartan-6, Virtex-6, Artix-7, Kintex-7, Virtex-7, Zynq

- 1 SPI input / 1 SPI output

- Compliant with DVB and ATSC standard

- Insertion of DTV-708 closed caption into payload of MPEG video elementary stream

-

Reed-Solomon Encoder

- Flexible RS Encoder meeting the requirements of most standards that employ RS codes including: IEEE 802.16, DVB-x, G.709, ETSI-BRAN, and CCSDS

- Supports continuous output data with no gap between code blocks

- Supports a code block length variable up to 4095 symbols with up to 256 check symbols

- Code block length and number of check symbols can be varied dynamically on a block by block basis

-

Reed-Solomon Decoder

- Flexible RS Decoder meeting the requirements of most standards that employ RS codes including: IEEE 802.16, DVB-x, G.709, ETSI-BRAN, and CCSDS

- Fully synchronous design using a single clock

- Supports continuous input data with no gap between code blocks

- Supports symbol size from 3 to 12 bits and any primitive field polynomial for a given symbol width