ARM Cortex-M0 Processor IP

Filter

Compare

4

IP

from

2

vendors

(1

-

4)

-

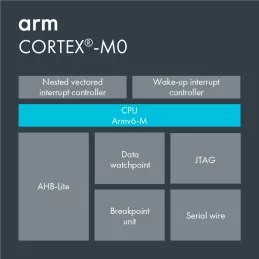

Small, Low Power, Energy Efficient 32-bit Microcontroller Processor

- Exceptional code density - on average, the mix between 16-bit and 32-bit instructions yields a better code density when compared to 8-bit and 16-bit architectures. This has significant advantages in terms of reduced memory requirements and maximizing the usage of precious on-chip Flash memory.

- Binary upward compatible with all other Cortex-M processors - the Cortex-M0 has mainly 16-bit Thumb-2 instructions and few 32-bit ones. These instructions are also present on all the other Cortex-M processors. Hence all code written for the Cortex-M0 will run as is on the other processors.

- Built-in low-power features - sleep, deep sleep and state retention are three low power modes available to the user

- Optional Debug Access Port and Serial Wire Debug - for devices where every pin counts the serial wire debug port uses only two pins

-

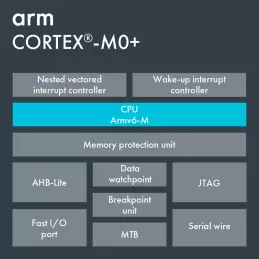

Arm Cortex-M0+

- Memory protection unit - Software reliability improves when each module is allowed access only to specific areas of memory required for it to operate. This protection prevents unexpected access that may overwrite critical data.

- Binary upward compatible with all other Cortex-M processors - The Cortex-M0+ has mainly 16bit Thumb-2 instructions and few 32bit ones. These instructions are also present on all the other Cortex-M processors. Hence all code written for the Cortex-M0+ will run as is on the other processors.

- Built-in low-power features - Sleep, deep sleep and state retention are three low power modes available to the user.

- Optional Debug Access Port and Serial Wire Debug - For devices where every pin counts the serial wire debug port uses only two pins.

-

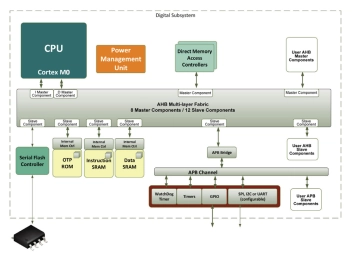

AHB Performance Subsystem - ARM Cortex M0

- The AHB Performance Subsystem is an AMBA® based system that is useful as the digital infrastructure for building low power SOCs needing additional performance.

- This AHB Multi-matrix system contains a flexible Power Management Unit for controlling power sequencing of the CPU and peripherals.

- The PMU can easily be extended to control additional cores, peripherals and even analog subsystems on the same SOC

-