ARM Cortex Processor IP

Filter

Compare

15

IP

from

8

vendors

(1

-

10)

-

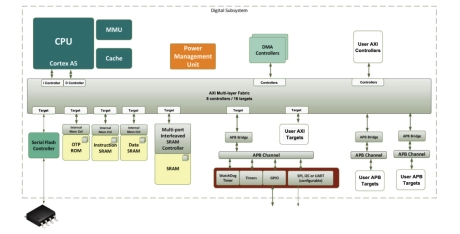

AXI Performance Subsystem - ARM Cortex A

- The AXI Performance Subsystem is an AMBA® AXI4 based system that is useful as the digital infrastructure for building SOCs needing high performance.

- This system contains an 8 Master component, 16 Slave component AXI4 multi-matrix for supporting multiple high speed user AXI Master components while providing high performance with Cortex-A5 class processors.

-

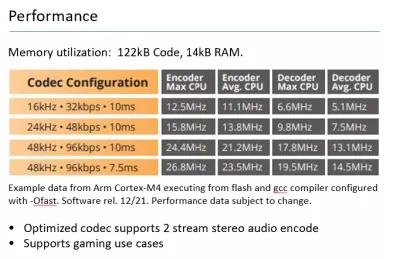

LC3 / LC3plus Bluetooth LE Audio Codecs for Arm Cortex M4 & M33

- Bluetooth SIG Qualified

- Production proven IP, extensively tested, commercially shipping

- High-Quality Audio with LC3 Codec

- • 7.5ms and 10ms frame lengths

-

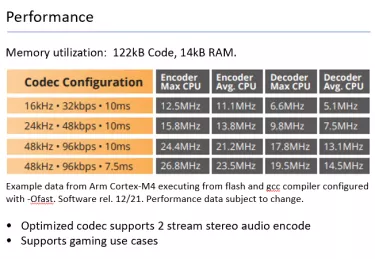

LC3 / LC3plus Bluetooth LE Audio Codecs for Arm Cortex M55

- Bluetooth SIG Qualified

- Production proven IP, extensively tested, commercially shipping

- High-Quality Audio with LC3 Codec

-

Machine Learning Processor

- Extending Performance and Efficiency

- Flexible Integration

- Unified Software and Tools

-

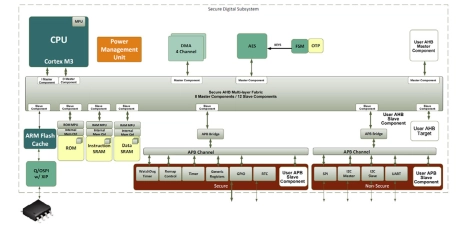

AHB Secure Subsystem - ARM Cortex M3

- The Secure AHB Performance Subsystem is a high-performance AHB subsystem that allows for a high level of hardware and software security.

- It integrates a security-conscious processor, the ARM Cortex-M3, with a security-conscious low power high-performance subsystem.

- Everything is pre-integrated with the necessary AHB and APB IP cores needed to run a small software kernel or a Real Time Operating System (RTOS).

-

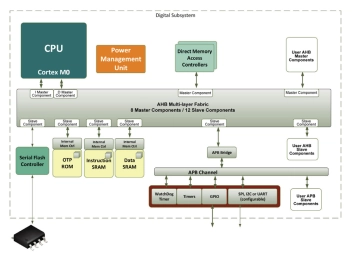

AHB Performance Subsystem - ARM Cortex M0

- The AHB Performance Subsystem is an AMBA® based system that is useful as the digital infrastructure for building low power SOCs needing additional performance.

- This AHB Multi-matrix system contains a flexible Power Management Unit for controlling power sequencing of the CPU and peripherals.

- The PMU can easily be extended to control additional cores, peripherals and even analog subsystems on the same SOC

-

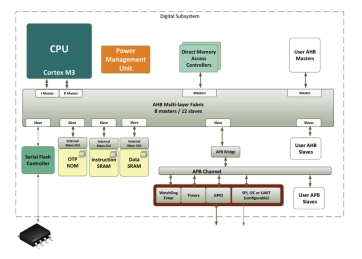

AHB Performance Subsystem - ARM Cortex M3

- The AHB Performance Subsystem is an AMBA® based system that is useful as the digital infrastructure for building low power SOCs needing additional performance.

- This AHB Multi-matrix system contains a flexible Power Management Unit for controlling power sequencing of the CPU and peripherals.

- The PMU can easily be extended to control additional cores, peripherals and even analog subsystems on the same SOC.

-

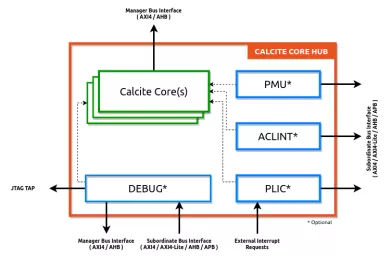

32b/64b RISC-V 5-stage, scalar, in-order, Application Processor. Linux and multi-core capable. Maps upto ARM A-35. Optimal PPA.

- 32/64 Bit RISC-V core

- 5-stage pipeline

- In-order, Single issue

- Multicore Capable (up to 8 cores)

-

Telematics Processors IP

- Core and infrastructure

- ? ARM® Cortex™-R4 MCU

- ? Embedded SRAM

- ? SDRAM controller

-

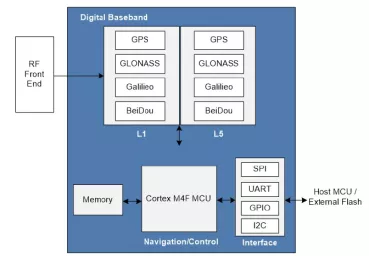

GNSS Ultra low power (GPS, Galileo, GLONASS, Beidou3, QZSS, IRNSS, SBAS) Digital IP

- Supports L1/E1 and L5/E5 bands for multiple constellations including GPS, Glonass, Galileo, Beidou

- Integrated Cortex ARM M4 F MCU

- Accuracy upto 1.5m CEP

- Multi-tone interference mitigation and pulsed interference mitigation