AMBA DMA IP

Filter

Compare

191

IP

from

32

vendors

(1

-

10)

-

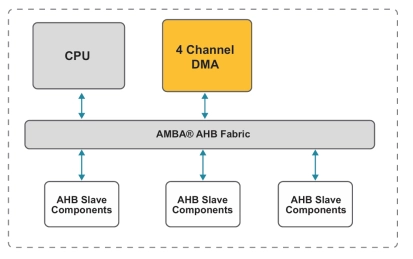

AMBA AHB 4 Channel DMA Controller

- The AHB 4 Channel DMA Controller is a multiple-channel direct memory access controller.

- The DMA IP Core is a Verilog HDL design that can be used in ASIC, Structured ASIC and FPGA designs.

- The design is intended to be used with AMBA based systems as a controller to transfer data directly from system memory to memory or system memory to peripheral device or IP Core.

-

PCIe 1.1 Controller supporting Root Port, Endpoint, Dual-mode Configurations, with Built-in DMA and Configurable AMBA AXI Interconnect

- PCIe Interface

- Supported silicon:

- AMBA AXI Interface

- Data Engine and Address translation for PCIe-to-AXI and AXI-to-PCIe transfers

-

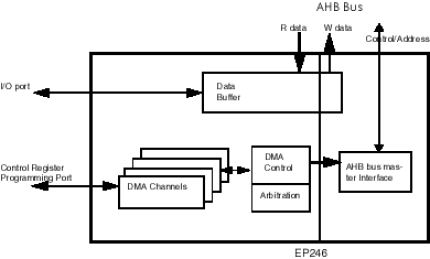

AMBA AHB Direct Memory Acess (DMA) Controller

- Multiple independent DMA channels with direct AHB bus interface.

- DMA transfers between AHB memory devices and I/O ports.

- Scatter-gather allows DMA to merge multiple data source to contiguous space.

- Supports both hardware initiated transfer and software initiated transfer.

-

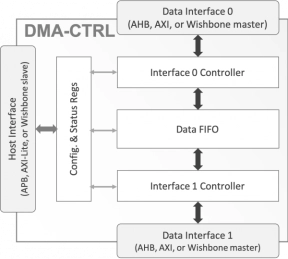

AHB/AXI/Wishbone DMA Controller

- The AXI4-SGDMA IP core implements a Host-to-Peripheral (H2P), or a Peripheral-to-Host (P2H) Direct Memory Access (DMA) engine, which interfaces the host system with an AXI4 Memory-Mapped master port and the peripheral with either a slave or a master AXI4-Stream port.

- The core operates in either Scatter-Gather (SG) Mode, reading descriptors from a run-time defined memory mapped-location, or in Direct Mode, transferring data according to a descriptor stored in local registers.

-

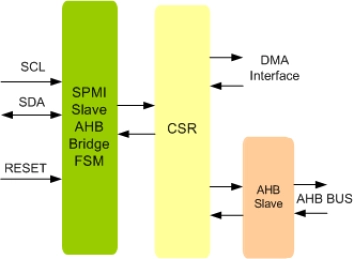

MIPI SPMI Slave DMA IIP

- Supports 2.0 and 1.0 MIPI SPMI Specification

- Full MIPI SPMI Slave functionality

- Supports following frames

- Command Frame

-

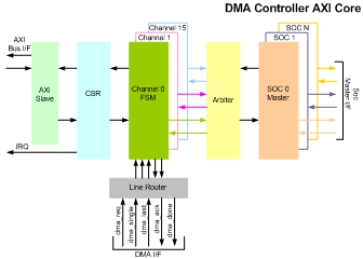

DMA Controller with AXI IIP

- Supports 1-16 channel DMA Transmit and DMA Receive Engine

- Supports latest ARM AMBA 3/4 AXI, AXI4-Lite, AMBA4 ACE, AMBA4 ACE-Lite, AXI4-Stream specification.

- Supports access for Ring and Chained Descriptor Structures

- Configurable Transmit and Receive Engine based on Host Memory Data Width

-

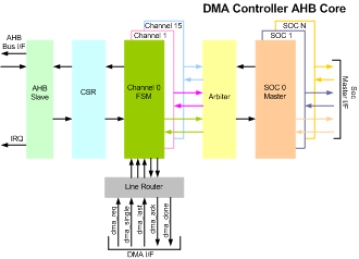

DMA Controller with AHB IIP

- Supports 1-16 channel DMA Transmit and DMA Receive Engine

- Compliant with ARM AMBA 2 AHB Specification

- Optional support for AMBA 3 AHB-Lite and AMBA 5 AHB Specification

- Supports access for Ring and Chained Descriptor Structures

-

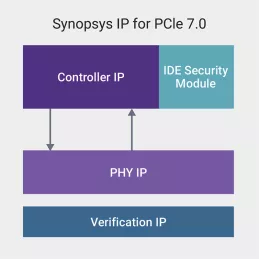

PCIe 6.0 (Gen6) Premium Controller with AMBA bridge and LTI & MSI Interfaces

- Supports all required features of the PCI Express 6.2/6.1/6.0.1 (64GT/s), 5.0 (32 GT/s), 4.0 (16 GT/s), 3.1 (8 GT/s) and PIPE (32-bit) specifications

- Based on silicon-proven PCIe 6.x controller design

- Allows a full 64GT/s x16 lane bandwidth with up to 1024-bit data path implementations

- Supports advanced RAS data protection features including ECC

-

PCIe 6.0 (Gen6) Premium Controller with AMBA bridge

- Supports all required features of the PCI Express 6.2/6.1/6.0.1 (64GT/s), 5.0 (32 GT/s), 4.0 (16 GT/s), 3.1 (8 GT/s) and PIPE (32-bit) specifications

- Based on silicon-proven PCIe 6.x controller design

- Allows a full 64GT/s x16 lane bandwidth with up to 1024-bit data path implementations

- Supports advanced RAS data protection features including ECC

-

PCIe 6.0 (Gen6) Premium Controller EP/RP/DM/SW 128-1024 bits with AMBA bridge and Advanced HPC Features (Arm CCA)

- Supports all required features of the PCI Express 6.2/6.1/6.0.1 (64GT/s), 5.0 (32 GT/s), 4.0 (16 GT/s), 3.1 (8 GT/s) and PIPE (32-bit) specifications

- Based on silicon-proven PCIe 6.x controller design

- Allows a full 64GT/s x16 lane bandwidth with up to 1024-bit data path implementations

- Supports advanced RAS data protection features including ECC