ADC IP

Filter

Compare

734

IP

from

99

vendors

(1

-

10)

-

6-bit, 12 GSPS Flash ADC - GlobalFoundries 22nm

- 6-bit resolution

- 12 GSPS sampling rate

- 10 GHz Input Bandwidth

- 13 mW Power

-

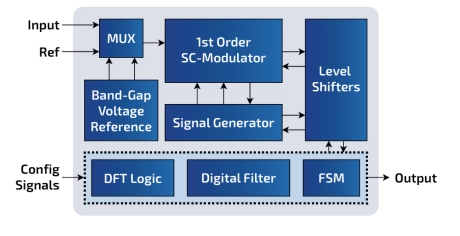

Voltage and Temperature Sensor with integrated ADC - GlobalFoundries® 22FDX®

- Voltage and temperature monitoring

- 3 single-ended voltage measurement inputs

- Operating temperature range: -40°C to 150°C

- Temperature measurement with accuracy up to 1°K ± 1°K change in temperature

-

14-bit 12.5MSPS SAR ADC - Tower 65nm

- The A14B12p5M is a high-performance, low-power analog-to-digital converter (ADC) intellectual property (IP) block designed for applications requiring both high speed and power efficiency.

- It offers 14-bit resolution with maximum sampling rate of 12.5 megasamples per second (MS/s), making it ideal for RF communications, radar sensing, and aerospace and defense applications.

-

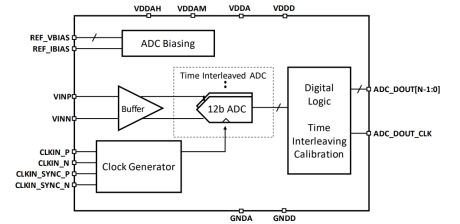

Ultra high-performance low-power ADC

- TSMC 28nm

- Ultra high-performance low-power ADC

- 12-bit ADC resolution

- Sampling rate up to 5GSPS

-

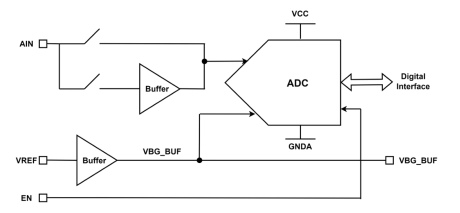

10-bit SAR ADC - XFAB XT018

- The TS_ADC_10b_X8 is a 10-bit capacitive successive approximation register (SAR) Analog-to-Digital converter (ADC).

- It operates with a 3.3 V analog power supply, a 1.8 V digital power supply, and an external voltage reference.

- The ADC converts single-ended input voltages and requires no external S/H circuit.

-

12-bit, 400 MSPS SAR ADC - TSMC 12nm FFC

- 12-bit Resolution

- 400 MSPS Sampling Rate

- 1 GHz Input Bandwidth

- Differential voltage input

- 4.2 mW Power

-

10-bit Pipeline ADC - Tower 180 nm

- 10-bit resolution

- 25 MSPS sampling rate

- 6 mW power

- 25 MHz Input Bandwidth

-

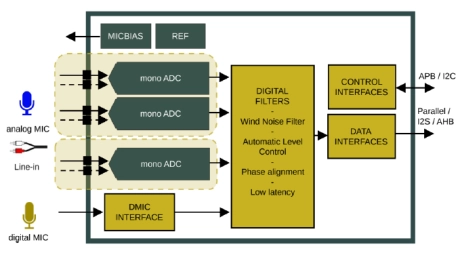

106dB, 24-bit audio three-channels ADC in TSMC 40uLP

- tADC106-SW1-LR.01_TSMC_40_uLP is a mixed (analog and digital) Virtual Component (ViC) in TSMC 40uLP containing a three-channel ADC and additional functions offering an ideal mixed signal front end for low power and high quality audio applications.

-

10Bit 25MHz sigma-delta ADC for VT sensor on SMIC 40nm

- The present IP is a single-ended 10-bit Sigma-Delta (SD) analog-to-digital converter

- This ADC operates with one 1.1V power supplies with low power consumption

- The 1.1V digital power supply is employed for easy integration with 1.1V digital signal processors and macro processors.

-

13-bit, 80 MSPS ADC - TSMC 65nm

- The A13B80M is a low-power, high-speed analog to digital converter (ADC) intellectual property (IP) design block.

- It is a hybrid-SAR ADC, with 13-bit resolution and a sampling speed of 80 megasamples per second (MSPS).