8K UHDTV Audio IP

Filter

Compare

169

IP

from

44

vendors

(1

-

10)

-

24bit 8K~ 96KHz Audio Codec High performance Silicon Proven DAC IP core

- 24bit Resolution

- Functional from -40 deg C to 125 deg C

- Reduces noise and power consumption.

- Provides accurate charge transfer without the need for calibration.

-

DisplayPort - Validates high-quality video and audio transmission for displays

- DisplayPort is a high-performance digital display interface designed for connecting computers, monitors, and other video devices. It supports high-definition and ultra-high-definition displays, offering top-tier video and audio transmission.

- In Verification IP (VIP), DisplayPort ensures the accurate functioning of display controllers, validating the transmission of video and audio data. VIP verifies compliance with DisplayPort standards, ensuring seamless integration with a wide range of devices.

-

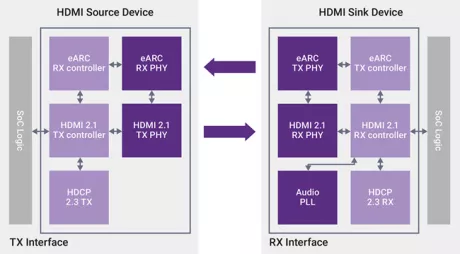

HDMI 2.1 Audio PLL in TSMC 16FFC 1.8V, North/South Poly Orientation

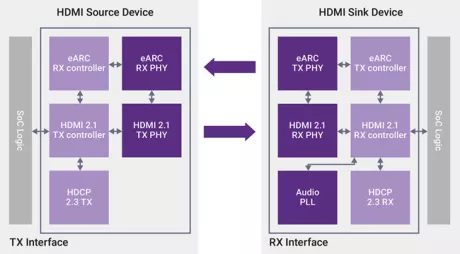

- HDMI 2.1 TX IP solution includes PHYs, controllers, HDCP embedded security modules, and verification IP

- Compliant with the HDMI 2.1, 2.0, 1.4, and HDCP 2.3, 1.4 specifications

- Support for key HDMI 2.1 features such as fixed-rate link capable of 48Gbps aggregate bandwidth, enhanced

- Metadata packets including dynamic HDR, eARC, auto low-latency mode, and variable refresh rate

-

HDMI 2.1 Audio PLL in TSMC 12FFC 1.8V, North/South Poly Orientation

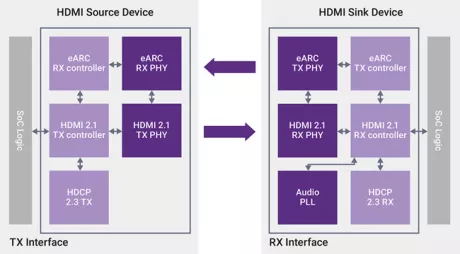

- HDMI 2.1 TX IP solution includes PHYs, controllers, HDCP embedded security modules, and verification IP

- Compliant with the HDMI 2.1, 2.0, 1.4, and HDCP 2.3, 1.4 specifications

- Support for key HDMI 2.1 features such as fixed-rate link capable of 48Gbps aggregate bandwidth, enhanced

- Metadata packets including dynamic HDR, eARC, auto low-latency mode, and variable refresh rate

-

HDMI 2.1 Audio PLL in SS 14LPP 1.8V, North/South Poly Orientation

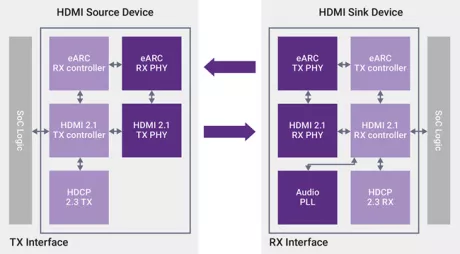

- HDMI 2.1 TX IP solution includes PHYs, controllers, HDCP embedded security modules, and verification IP

- Compliant with the HDMI 2.1, 2.0, 1.4, and HDCP 2.3, 1.4 specifications

- Support for key HDMI 2.1 features such as fixed-rate link capable of 48Gbps aggregate bandwidth, enhanced

- Metadata packets including dynamic HDR, eARC, auto low-latency mode, and variable refresh rate

-

HDMI 2.1 Audio PLL in TSMC (16nm, 12nm)

- Quad-pixel interface allows up to 48Gbps bandwidth data for uncompressed 8K resolution with 60Hz refresh rate

- Fixed-rate stream with 16b18b decoding and de-scrambling

- Supports latest object-based audio formats with 1536kHz sample rate and up to 32 channels

- Dynamic metadata packets reception

-

HDMI 2.1 Audio PLL in Samsung (14nm)

- Quad-pixel interface allows up to 48Gbps bandwidth data for uncompressed 8K resolution with 60Hz refresh rate

- Fixed-rate stream with 16b18b decoding and de-scrambling

- Supports latest object-based audio formats with 1536kHz sample rate and up to 32 channels

- Dynamic metadata packets reception

-

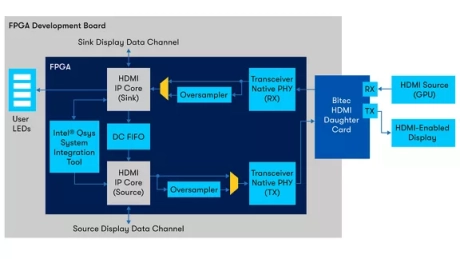

HDMI Intel® FPGA IP Core

- The HDMI Intel FPGA intellectual property (IP) core provides support for the next generation of video display interface technology

- Due to its ability to send high-definition audio and video, High-Definition Multimedia Interface (HDMI) has become the most common digital connection in consumer electronics.

-

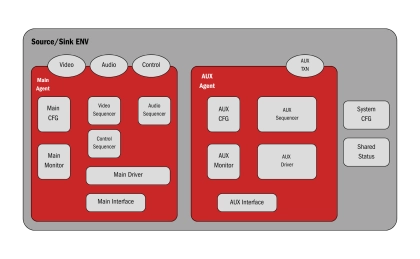

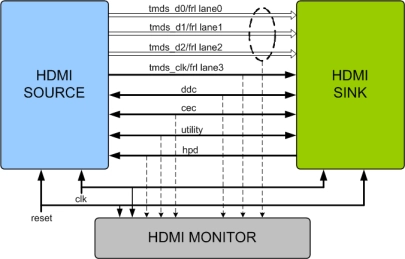

HDMI 1.4/2.0/2.1 Verification IP

- Protocol Checker fully compliant with HDMI Specification 1.4b, 2.0b and 2.1 compliant.

- Full HDMI source and sink device functionality

- Supports Video data coding.

- Supports TERC4 coding and Control period codings.

-

HDMI 2.1 Quad-Pixel Tx Controller

- HDMI 2.1 TX IP solution includes PHYs, controllers, HDCP embedded security modules, and verification IP

- Compliant with the HDMI 2.1, 2.0, 1.4, and HDCP 2.3, 1.4 specifications

- Support for key HDMI 2.1 features such as fixed-rate link capable of 48Gbps aggregate bandwidth, enhanced

- Metadata packets including dynamic HDR, eARC, auto low-latency mode, and variable refresh rate