7nm Combo PHY IP

Filter

Compare

7

IP

from

5

vendors

(1

-

7)

-

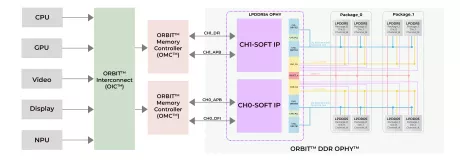

LPDDR5X/5/4X/4 combo PHY at 7nm

- Compliant with JEDEC JESD209-5B for LPDDR5X/5/4X/4 with PHY standards

- Delivering up to 8533Mbps

- DFI 5.1 specification PHY Interface Compliant

- Support up to 4 ranks

-

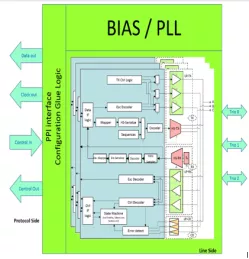

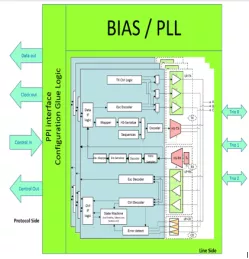

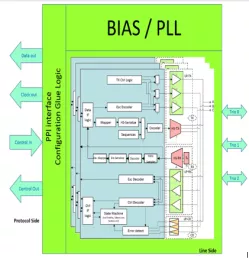

MIPI C/D-PHY Combo Rx IP, Silicon Proven in TSMC 7 FF

- Compliant with MIPI D-PHY spec up to v2.5 and C-PHY spec up to v2.0

- Support both MIPI DSI and CSI-2 protocols

- Support HS data rate up to 6Gbps ( 6Gsps ) per lane (per trio)

- Support LS data rate of 10Mbps and Ultra-low power mode

-

MIPI C/D-PHY Combo Tx IP, Silicon Proven in TSMC 7 FF

- Compliant with MIPI D-PHY spec up to v2.5 and C-PHY spec up to v2.0

- Support both MIPI DSI and CSI-2 protocols

- Support HS data rate up to 6Gbps ( 6Gsps ) per lane (per trio)

- Support LS data rate of 10Mbps and Ultra-low power mode

-

MIPI C-PHY/D-PHY Combo v1.2 IP in TSMC(5nm, 7nm, 12/16nm, 28nm and 40nm)

- Fully compliant with MIPI D-PHY v1.2 and C-PHY v1.0 spec

- Supports MIPI CSI-2 protocol

-

LPDDR4x/5 Secondary/Slave (memory side!) PHY

- Supports JEDEC standard LPDDR5, LPDDR4X, LPDDR4

- Secondary side PHY

- Custom implementations available

-

ONFI_4 IO Pad Set

- ONFI Single-Ended Driver / Receiver Features:

- ? Driver – user-selectable on-die termination and programmable drive strength with ODT / ZO calibration and programmable “off” state control.

- o ODT Rtt = 30? / 50? / 75? / 100? / 150?

- o ZOUT = 18? / 25? / 35? / 50?

-

MIPI D-PHY Rx IP, Silicon Proven in TSMC 7FF

- Compliant with MIPI D-PHY spec up to v2.5 and C-PHY spec up to v2.0

- Support both MIPI DSI and CSI-2 protocols

- Support HS data rate up to 6Gbps ( 6Gsps ) per lane (per trio)

- Support LS data rate of 10Mbps and Ultra-low power mode