40/100 Gigabit Ethernet MAC IP

Filter

Compare

12

IP

from

9

vendors

(1

-

10)

-

Gigabit Ethernet MAC IP Core

- The silicon-proven Gigabit Ethernet IP core provides a 10/100 Mbps Media Independent Interface (MII) and a 1000 Mbps Gigabit Media Independent Interface (GMII).

- It also supports optional Reduced MII (RGMII), and Serial GMII (SGMII).

-

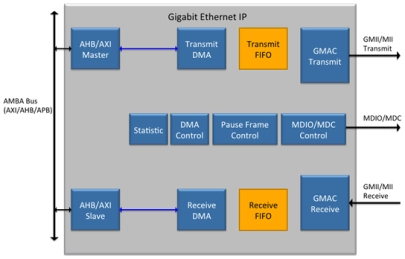

Gigabit Ethernet Controller

- XEC is a high performance 1000M/100M/10M Ethernet Controller IP. It support GMII/RGMII/MII/RMII MAC-PHY interface and support AXI/AHB system bus.

- XEC can receive the data from Ethernet PHY to the AXI/AHB bus, and to send out data from AXI/AHB bus to the Ethernet PHY.

-

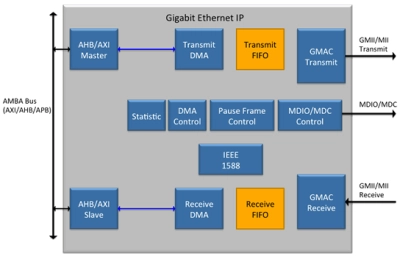

Gigabit Ethernet with IEEE 1588 and AVB

- The Gigabit Ethernet Media Access Controller IP is compliant with the Ethernet IEEE 802.3-2008 standard and supports protocol extensions for Audio Video Bridging (AVB).

- The Gigabit Ethernet IP provides a 10/100 Mbps Media Independent Interface (MII) and a 1000 Mbps Gigabit Media Independent Interface (GMII).

-

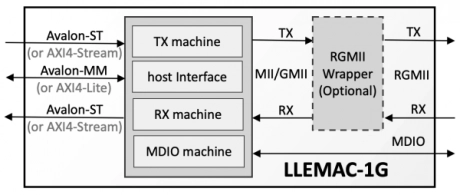

Low-Latency 10/100/1000 Ethernet MAC

- The LLEMAC-1G implements an Ethernet Media Access Controller (MAC) compatible with the 10/100 Mbps IEEE 802.3 and 1Gbps IEEE 802.3-2002 specifications.

- Featuring extremely low egress and ingress latency, the core is ideal for the implementation of TSN Ethernet nodes, live streaming and other devices requiring minimum latency in the reception and transition of Ethernet frames.

-

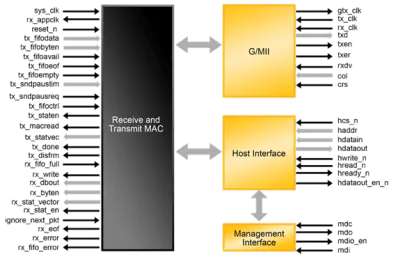

Ethernet MAC Cores

- Compliant to IEEE 802.3z Standard

- Generic Host Interface

- Configurable 8-bit or 16-bit and Greater Data Bus

- 16-bit Wide Internal Data Path

-

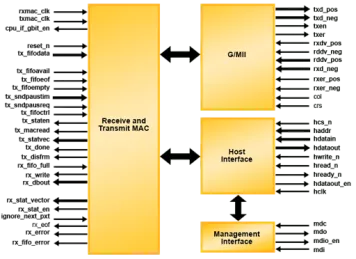

Tri-Speed Ethernet MAC Core IP

- Compliant to IEEE 802.3z standard

- Generic 8-bit host interface

- 8-bit wide internal data path

- Generic transmit and receive FIFO interface

-

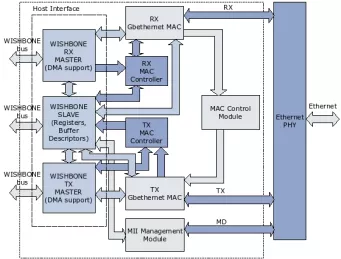

MAC 10/100/1000 Ethernet Controller

- IEEE 802.3-2002 specification with preamble, start-of-frame delimiter (SFD), frame padding generation and cyclic redundancy code (CRC) generation and checking is fully implemented

- Supports 10/100 Mbps or 1000 Mbps operation (selectable via a core configuration registers)

- Supports full- and half-duplex operation (selectable via a core configuration registers)

- CSMA/CD protocol for half-duplex operation

-

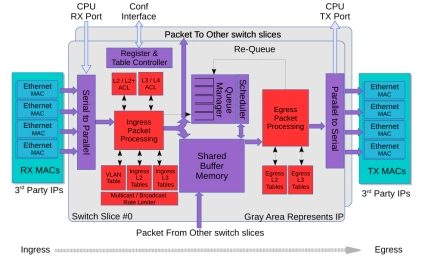

Ethernet Switch/Router Datacenter ToR 32x100G

- 32 x 100 Gigabit Ethernet ports.

- Full wire-speed on all ports and all Ethernet frame sizes.

- Store and forward shared memory architecture.

- Support for jumbo packets up to 32738 bytes.

-

Ethernet Device Driver

- The 802.3 Ethernet Device Driver is developed to support both the 10/ 100 Ethernet IP as well as its Gigabit Ethernet IP.

- The device driver provides communications between the MAC (Medium Access Control) and the OS (Operating System) as well as access to the overlying network layer protocol and the applications layer.

-

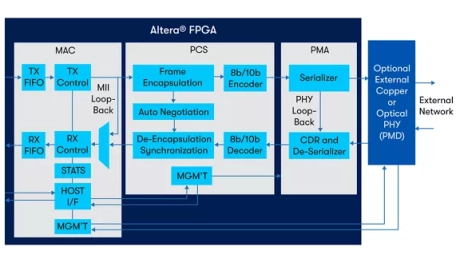

Triple-Speed Ethernet FPGA IP

- The Triple-Speed Ethernet FPGA IP core consists of a 10/100/1000 Mbps Ethernet media access control (MAC) and physical coding sublayer (PCS) Intellectual Property (IP).

- This IP function enables FPGAs to interface to an external Ethernet PHY device, which interfaces to the Ethernet network.