3D I/O IP

Filter

Compare

17

IP

from

10

vendors

(1

-

10)

-

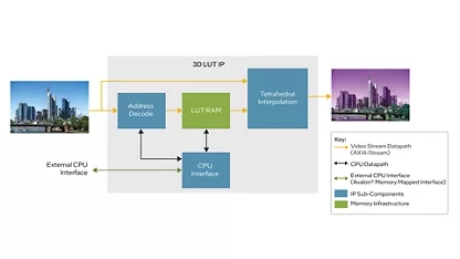

3D LUT Intel® FPGA IP

- As a part of the Video and Vision Processing (VVP) Suite Intel® FPGA IP, the 3D look-up table (LUT) Intel® FPGA IP provides an efficient solution for video color space and dynamic range conversions, chroma keying, and the creation of artistic effects.

-

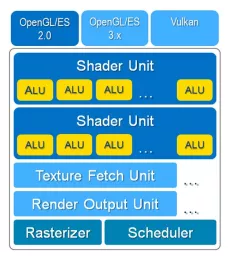

OpenGL ES 2.0 3D graphics IP core for FPGAs and ASICs

- D/AVE NX is the latest and most powerful addition to the D/AVE family of rendering cores.

- It is the first IP to bring 3D graphics OpenGL ES 2.0 rendering (with some ES 3.0 / 3.1 extensions) to the FPGA and SoC world and – with offline-shader compilers – even into MCUs or low-end MPUs with small amounts of memory and bare-metal or RTOS operation systems.

-

OpenGL® ES2.0 compatible 3D graphics IP core

- The smallest class 3D graphics IP core, 0.48mm² in silicon footprint

- Full OpenGL ES 2.0 capability

- Ultra-low power consumption

-

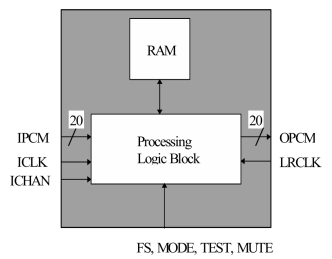

3-D Audio Processing Core

- The J5 is a core cell design of an application specific signal processor which performs both Trusurround(TM) and SRS® 3-D audio virtualization processing in a single design.

- The 3-D processing allows users to enjoy benefits of a multi-channel sound source with only two reporduction channels.

-

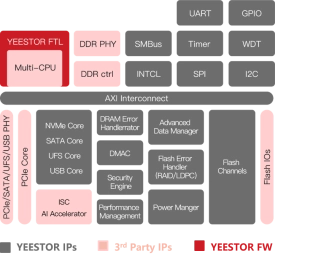

NVMe SSD Controller Platform

- The PCIe-NVMe SSD controller platform is compliant with NVM Express 1.2 specification and targets for both enterprise and client SSD markets.

- It features YEESTOR's NVMe controller core and LDPC error correction core to enable low-power and cost-effective SSD controllers that support 1x/1y/1z MLC/TLC and 3D NAND.

-

UCIe-S 64GT/s PHY IP

- The UCIe-S 64GT/s PHY IP is a cutting-edge solution designed to meet the growing demand for ultra-high-speed interconnects between dies in standard packaging environments.

- Leveraging the UCIe (Universal Chiplet Interconnect Express) 3.0 standard, this IP supports a blistering data rate of up to 64Gbps per lane, enabling next-generation AI, HPC, and data center SoC applications.

-

UCIe-A 64GT/s PHY IP

- The UCIe-A 64GT/s PHY IP is a cutting-edge solution designed to meet the growing demand for ultra-high-speed interconnects between dies in advanced packaging environments.

- Leveraging the UCIe (Universal Chiplet Interconnect Express) 3.0 standard, this IP supports a blistering data rate of up to 64Gbps per lane, enabling next-generation AI, HPC, and data center SoC applications.

-

TSMC N3P Source Sync 3DIO PHY

- Synopsys 3DIO IP Solution is a specialized IO for multi-die integration

- It includes multiple IP offerings for system-on-chip (SoC) designers to implement tunable, integrated multi-die design structures targeting HPC (AI), GPU, CPU, and mobile applications

- The optimal area of the 3DIO IP is carefully designed to be within the BUMP, providing significant advantages in implementation and signal routing

- Synopsys 3DIO IP Solution is architected to support 2.5D, 3D and SoIC package form factors, with flexible physical dimensions on u-BUMP or TSV integration

-

TSMC N3P Source Sync 3DIO Library

- Synopsys 3DIO IP Solution is a specialized IO for multi-die integration

- It includes multiple IP offerings for system-on-chip (SoC) designers to implement tunable, integrated multi-die design structures targeting HPC (AI), GPU, CPU, and mobile applications

- The optimal area of the 3DIO IP is carefully designed to be within the BUMP, providing significant advantages in implementation and signal routing

- Synopsys 3DIO IP Solution is architected to support 2.5D, 3D and SoIC package form factors, with flexible physical dimensions on u-BUMP or TSV integration