112Gbps IP

Filter

Compare

36

IP

from

6

vendors

(1

-

10)

-

100G SerDes PAM4 PHY

- The SERDES PHY IP delivers a high-performance, low-power solution for high-speed interfaces up to 112Gbps.

- It supports diverse applications including AI accelerators, data centers, 5G infrastructure, and automotive SoCs.

-

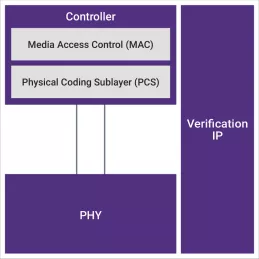

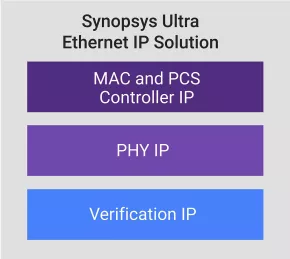

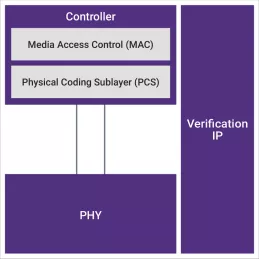

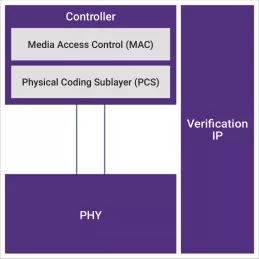

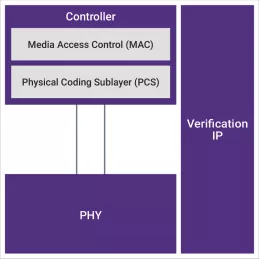

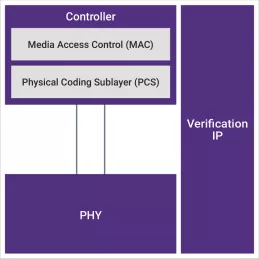

Complete 1.6T Ultra Ethernet IP Solution

- Ethernet MAC, PCS and PHY to complete a full Ultra Ethernet interface stack

- Supports evolving IEEE 802.3 and OIF-224G electrical standards

- Provides support for 4 x 400G, 2 x 800G, and 1.6T Ethernet rates using 112Gbps and 224Gbps SerDes

- Meets performance criteria for chip-to-chip, chip-to-module, and long reach copper/backplane interconnects

-

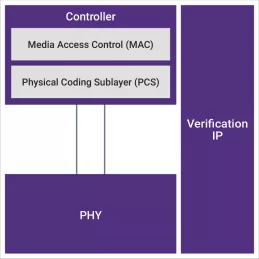

112G PHY, TSMC N7 x4, North/South (vertical) poly orientation

- Supports full-duplex 1.25 to 112Gbps data rates in several lane configurations

- Enables 100G, 200G, 400G, 800G Ethernet interconnects for wired and optical network infrastructure

- Supports IEEE 802.3ck and OIF standards electrical specifications

- Meets the performance requirements of multi-die, co-packaged optics, near-packaged optics, chip-to-chip, chip-to-module, and backplane interconnects

-

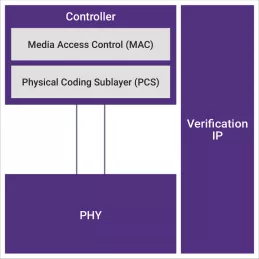

112G Ethernet PHY, TSMC N7 x4, North/South (vertical) poly orientation

- Supports full-duplex 1.25 to 112Gbps data rates in several lane configurations

- Enables 100G, 200G, 400G, 800G Ethernet interconnects for wired and optical network infrastructure

- Supports IEEE 802.3ck and OIF standards electrical specifications

- Meets the performance requirements of multi-die, co-packaged optics, near-packaged optics, chip-to-chip, chip-to-module, and backplane interconnects

-

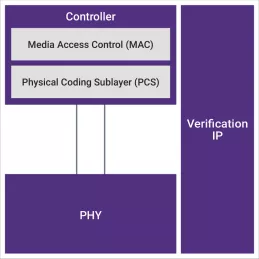

112G Ethernet PHY, TSMC N7 x2, North/South (vertical) poly orientation

- Supports full-duplex 1.25 to 112Gbps data rates in several lane configurations

- Enables 100G, 200G, 400G, 800G Ethernet interconnects for wired and optical network infrastructure

- Supports IEEE 802.3ck and OIF standards electrical specifications

- Meets the performance requirements of multi-die, co-packaged optics, near-packaged optics, chip-to-chip, chip-to-module, and backplane interconnects

-

112G Ethernet PHY, TSMC N7 x1, North/South (vertical) poly orientation

- Supports full-duplex 1.25 to 112Gbps data rates in several lane configurations

- Enables 100G, 200G, 400G, 800G Ethernet interconnects for wired and optical network infrastructure

- Supports IEEE 802.3ck and OIF standards electrical specifications

- Meets the performance requirements of multi-die, co-packaged optics, near-packaged optics, chip-to-chip, chip-to-module, and backplane interconnects

-

112G Ethernet PHY, TSMC N6 x2, North/South (vertical) poly orientation

- Supports full-duplex 1.25 to 112Gbps data rates in several lane configurations

- Enables 100G, 200G, 400G, 800G Ethernet interconnects for wired and optical network infrastructure

- Supports IEEE 802.3ck and OIF standards electrical specifications

- Meets the performance requirements of multi-die, co-packaged optics, near-packaged optics, chip-to-chip, chip-to-module, and backplane interconnects

-

112G Ethernet PHY, TSMC N6 x1, North/South (vertical) poly orientation

- Supports full-duplex 1.25 to 112Gbps data rates in several lane configurations

- Enables 100G, 200G, 400G, 800G Ethernet interconnects for wired and optical network infrastructure

- Supports IEEE 802.3ck and OIF standards electrical specifications

- Meets the performance requirements of multi-die, co-packaged optics, near-packaged optics, chip-to-chip, chip-to-module, and backplane interconnects

-

112G Ethernet PHY, TSMC N5 x4, North/South (vertical) poly orientation

- Supports full-duplex 1.25 to 112Gbps data rates in several lane configurations

- Enables 100G, 200G, 400G, 800G Ethernet interconnects for wired and optical network infrastructure

- Supports IEEE 802.3ck and OIF standards electrical specifications

- Meets the performance requirements of multi-die, co-packaged optics, near-packaged optics, chip-to-chip, chip-to-module, and backplane interconnects

-

112G Ethernet PHY, TSMC N3P x4 1.2V, North/South (vertical) poly orientation

- Supports full-duplex 1.25 to 112Gbps data rates in several lane configurations

- Enables 100G, 200G, 400G, 800G Ethernet interconnects for wired and optical network infrastructure

- Supports IEEE 802.3ck and OIF standards electrical specifications

- Meets the performance requirements of multi-die, co-packaged optics, near-packaged optics, chip-to-chip, chip-to-module, and backplane interconnects