112G Long-Reach SerDes IP

Filter

Compare

2

IP

from

2

vendors

(1

-

2)

-

112G Multi-SerDes

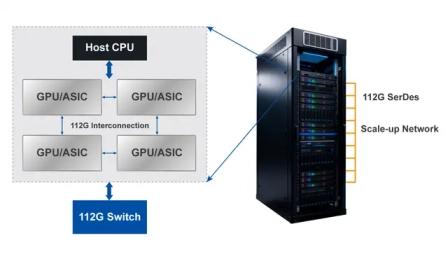

- Designed with a small footprint, ultra-low latency, and low power consumption, the 112G SerDes maximizes bidirectional memory access efficiency, reduces software complexity, and helps chip developers leverage existing Ethernet infrastructure to significantly lower Total Cost of Ownership (TCO).

- Featuring IEEE 802.3-compliant Forward Error Correction (FEC), 35dB ultra-high channel loss compensation, and adaptive high-speed equalization technologies (CTLE, FFE), it provides full-cycle link protection—from error correction to pre-warning—enabling highly compatible, stable, and efficient chip-to-chip connectivity solutions.

-

112G-ULR PAM4 SerDes PHY

- Supports full-duplex 1.25Gbps to 112.5Gbps data rates

- Superior bit error rate (BER) performance across high-loss and reflective channels

- Compliant with IEEE 802.3ck and OIF standard electrical specifications

- Supports flexible SoC floorplan and IP placement and provides package substrate guideline/reference designs