ESD Protection IP for TSMC

Welcome to the ultimate

ESD Protection IP

for

TSMC

hub! Explore our vast directory of

ESD Protection IP

for

TSMC

All offers in

ESD Protection IP

for

TSMC

Filter

Compare

6

ESD Protection IP

for

TSMC

from

3

vendors

(1

-

6)

Filter:

- 28nm

-

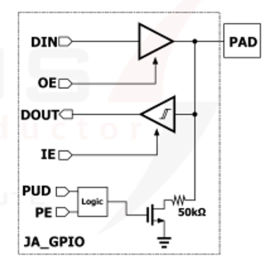

1.8V Capable GPIO on Samsung Foundry 4nm FinFET

- The 1.8V capable GPIO is an IP macro for on-chip integration. It is a 1.8V general purpose I/O built with a stack of 1.2V MOS FINFET devices. It is controlled by 0.75V (core) signals.

- Supported features include core isolation, output enable and pull enable. Extra features such as input enable/disable, programmable drive strength and pull select, can be supported upon request.

-

ESD Solutions for Multi-Gigabit SerDes in TSMC 28nm

- A Wirebond and FlipChip compatible <80fF ESD Solutions for Multi-Gigabit SerDes Applications.

- This silicon-proven TSMC 28nm Digital I/O Library delivers a low-capacitance, high-reliability interface solution optimized for advanced semiconductor applications.

- Featuring low-capacitance LVDS differential pairs (<250fF per pin) at 0.8V, this library ensures superior signal integrity for high-speed applications.

-

High-Speed 3.3V I/O library with 8kV ESD Protection in TSPCo 65nm

- A 3.3V wirebond I/O library with 8kV HBM ESD protection, a 1.2Gbps LVDS, GPIO, and I2C compliant ODIO in an ultra-small footprint.

- This library ensures robust reliability in challenging environments, with capabilities including 8kV HBM, 500V CDM, and a robust 2kV IEC 61000-4-2 system stress capability.

- Its compact footprint makes it ideal for applications where size is critical.

-

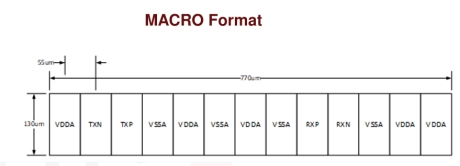

A 28nm 1.8V-3.3V Fail-Safe General-Purpose IO & OSC

- Fail-Safe GPIO in TSMC 28nm process technology

- Physical features

- This library also features a 33MHz OSC (3.3V).

-

High-voltage solutions in baseline GlobalFoundries and multi-foundry technologies

- High-Voltage ESD

- Physical Features

-

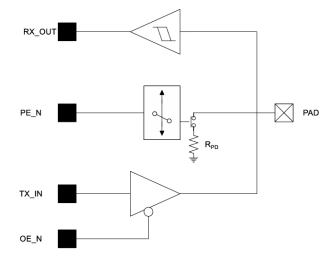

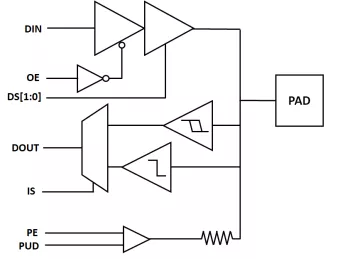

3.3V Wide-Range General Purpose I/O Pad Set

- ? Multi-Voltage (1.8V, 2.5V, 3.3V)

- ? LVCMOS / LVTTL input with selectable hysteresis

- ? Programmable drive strength (rated 2mA to 12mA)

- ? Selectable output slew rate