DDR4 IP for TSMC

Welcome to the ultimate

DDR4 IP

for

TSMC

hub! Explore our vast directory of

DDR4 IP

for

TSMC

All offers in

DDR4 IP

for

TSMC

Filter

Compare

5

DDR4 IP

for

TSMC

from

3

vendors

(1

-

5)

Filter:

- 16nm

-

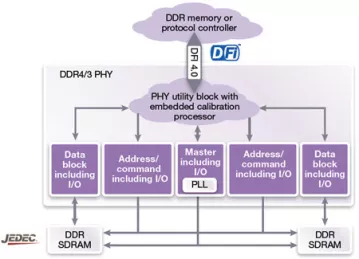

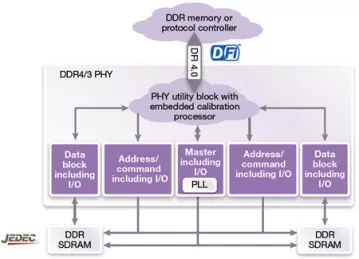

DDR4/3 PHY - TSMC 16FFC

- Supports JEDEC standard DDR4, DDR3, and DDR3L SDRAMs

- High-performance DDR PHY supporting data rates up to 3200 Mbps

- Compatible with JEDEC compliant DDR3/4 UDIMMs and RDIMMs as well as DDR4 LRDIMMs

- Supports up to 16 logical ranks for high capacity memory requirements

-

DDR4/3 PHY - TSMC 16FF+GL

- Supports JEDEC standard DDR4, DDR3, and DDR3L SDRAMs

- High-performance DDR PHY supporting data rates up to 3200 Mbps

- Compatible with JEDEC compliant DDR3/4 UDIMMs and RDIMMs as well as DDR4 LRDIMMs

- Supports up to 16 logical ranks for high capacity memory requirements

-

DDR5/4 PHY - TSMC 16FFC

- Supports JEDEC standard DDR5 and DDR4 SDRAMs

- High-performance DDR PHY supporting data rates up to 8400 Mbps

- PHY independent, firmware-based training using an embedded calibration processor

- Supports up to 4 trained states/ frequencies with <3μs switching time

-

DDR PHY

- Dolphin's hardened DDR4/3/2 SDRAM PHY and LPDDR5/4x/4/3/2 SDRAM PHY IP is a silicon-proven, Combo PHY supporting speeds up to 4266 Mbps.

- It is fully compliant with the DFI 4.0 specification, and features include slew rate control, per-bit de-skew, gate training, read and write leveling and built-in self test (BIST).

- In addition, our PHY IP is optimized to provide a complete solution when combined with Dolphin's DDRx and LPDDRx SDRAM Memory Controller IP.

-

LPDDR PHY

- Application-optimized configurations for fast time to delivery and lower risk

- Low-power VDD idle, VDD light sleep, and power-efficient clocking in low-speed modes

- I/O pads with impedance calibration logic and data-retention capability

- Fine-grain custom delay cell for delay tuning

- Internal and external datapath loop-back modes

- RX and TX equalization for heavily loaded systems

- Programmable per-bit (PVT compensated) deskew on read and write datapaths