Analog Subsystem IP for GLOBALFOUNDRIES

Welcome to the ultimate

Analog Subsystem IP

for

GLOBALFOUNDRIES

hub! Explore our vast directory of

Analog Subsystem IP

for

GLOBALFOUNDRIES

All offers in

Analog Subsystem IP

for

GLOBALFOUNDRIES

Filter

Compare

7

Analog Subsystem IP

for

GLOBALFOUNDRIES

from

3

vendors

(1

-

7)

Filter:

- 12nm

-

-

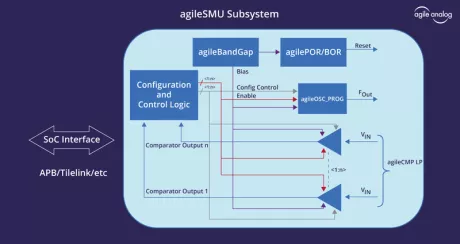

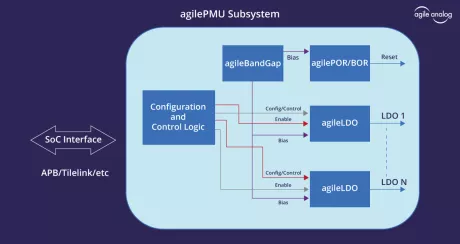

Power Management Subsystem

- The agilePMU Subsystem is an efficient and highly integrated Power Management Unit for SoCs/ASICs.

- Featuring a Power-On-Reset (POR), multiple Low Drop-Out (LDO) regulators, and an associated reference generator.

- The agilePMU Subsystem is designed to ensure low power consumption while providing optimal power management capabilities.

-

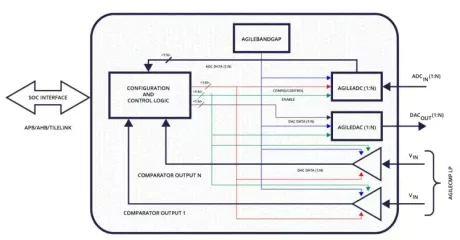

Sensor Interface Subsystem

- The agileSensorIF Subsystem is an efficient and highly integrated sensor interface for SoCs/ASICs.

- Featuring multiple Analog-to-Digital Converters (agileADC), Digital-to-Analog Converters (agileDAC), low-power programmable analog comparators (agileCMP_LP), and an associated reference generator (agileREF).

- The agileSensorIF Subsystem enables easy interaction with the analog world.

-

UCIe based 8-bit 48-Gsps Transceiver (ADC/DAC/PLL/UCIe)

- 48-Gsps peak sample rate

- 8 bit resolution

- UCIe SP (16x lanes at 16Gbps) with streaming controller

-

UCIe based 12-bit 12-Gsps Transceiver (ADC/DAC/PLL/UCIe)

- 12-Gsps peak sample rate

- 12 bit resolution (programmable)

- UCIe SP (16x lanes at 16Gbps) with streaming controller

-

8-bit 48-Gsps Transceiver (ADC/DAC/DLL)

- 48-Gsps peak sample rate

- 8 bit resolution

- SMALLER than competing solutions

- LOWER POWER than competing solutions