S21 Area optimized 64-bit RISC V processor

Overview

The SiFive S21 Standard Core is a full-featured 64-bit embedded processor based on the S2 Series. The S21 has separate Instruction and Data Buses, along with 2 banks of Tightly Integrated Memory (TIMs). The S21 is an ideal choice for area constrained applications demanding a 64-bit processor.

Key Features

- RISC-V ISA - RV64IMAC

- 64-bit AXI Ports

- Machine and User Mode with 4 Region Physical Memory Protection

- 3-stage pipeline with Simultaneous Instruction and Data Access

- 2 Banks of Tightly Integrated Memory

- CLIC interrupt controller with 127 interrupts

- Advanced debug with 4 hardware breakpoints/watchpoints

- 1.6 DMIPS/MHz

- 3.2 Coremarks/MHz

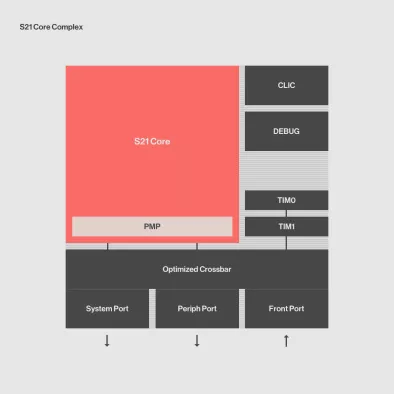

Block Diagram

Deliverables

- RTL Evaluation

- Test Bench RTL

- Software Development Kit

- FPGA Bitstream

- Documentation

Technical Specifications

Short description

S21 Area optimized 64-bit RISC V processor

Vendor

Vendor Name

Related IPs

- S51 Low-power 64-bit MCU RISC V core

- S54 64-bit embedded RISC V processor

- E31 Balanced performance and efficiency RISC V core

- Optimized for GHz+ operating speeds with minimum area and power consumption, ARC HS Processors are ideal for very high-performance embedded applications

- 64-bit CPU with Modern RISC Architecture, MemBoost and PMA

- Power & area optimized: 2–3-stage, single-issue pipeline, as small as 13.5k gates