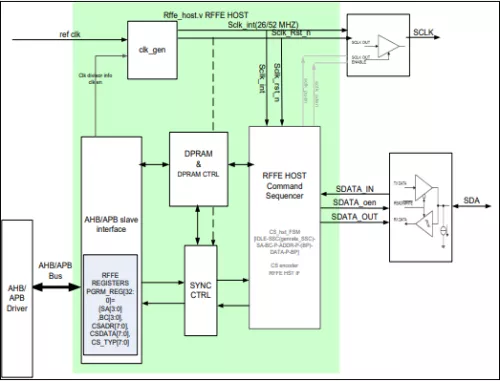

Mobile radio communication systems are complex multi-radio systems comprising several transceivers. Arasan supports the latest MIPI RFFE standard v3.0. The RFFE bus is a 2-wire serial interface that utilizes a bus frequency of up to 52 MHz and timing accurate trigger mechanisms to allow control of timing-critical functions. It is used to connect a digital RFIC to RF front-end components, like Power Amplifiers, Low-Noise Amplifiers, and Antenna Sensors, which are considered RFFE Slaves.

The RFFE Master v3.0 IP core typically resides in the RFIC in a mobile platform, and utilizes the RFFE bus to identify, program, and monitor the registers in RF front end Slave devices through programmed IO. It is designed to support existing standards such as LTE, UMTS, HSPA, and EGPRS, and is usable in configurations ranging from single Master/single Slave to multi-Master/multi-Slave.

At a minimum, Arasan delivers RFFE Master in RTL form. Physical designs of the complete RFFE Master, including the Pad Logic block for CLK and DATA as shown below, can be provided upon request.

MIPI RFFE Master Controller IP Core v3.0

Overview

Key Features

- Compliant with MIPI RFFE Specification 3.0

- Delivered in Reuse Methodology Manual (RMM) compliant Verilog RTL format

- Optionally delivered as a physical design

- Small footprint

- Up to 15 Devices can be connected per RFFE bus

- Low pin count on RFFE interface (SCLK and SDATA)

- Low EMI

- Low power consumption

- RFFE clock speed of 52 MHz

- Supports all Mandatory features required for RFFE Master as specified in the MIPI RFFE Specification.

- Can be easily customized to add additional optional features.

- Backward compatible with RFFE v2.0 master core IP and v1.0 master core IP

Benefits

- Fully compliant to MIPI RFFE standard

- Small footprint

- Code validated with Spyglass

- Functionality ensured with comprehensive verification

- Premier direct support from Arasan IP core designers

Block Diagram

Deliverables

- IP Deliverables for Digital Core

- Verilog HDL of the IP Core

- User guide

- Gate count estimates available upon request

- Synthesis scripts

- Simulation environment including test bench, BFM’s, and exhaustive test suite

- Additional Deliverables, for Physical Design (optional)

- GDS-II Database

- LVS Netlist

- Physical Abstract Models (LEF)

- Timing Models (LIB)

Technical Specifications

Maturity

Silicon proven

Availability

Now